我们将在本教程中了解EX或Gate。EX或GATE是独家或门。这并不经常被用作包容性或门,只不过是常规或门。XOR门具有自己的意义。我们将学习XOR门的符号,真实表,使用其他门(以及,或,NAND,NOR),流行的XOR IC以及独占或门(XOR门)的一些重要应用。

异或门简介

独占或门,也称为EX或门或XOR门,是一种重要的数字逻辑门,它实现了一个独占或逻辑,即当且仅当其中一个输入为HIGH时,输出为HIGH。如果两个输入都是LOW或HIGH,则输出为LOW。

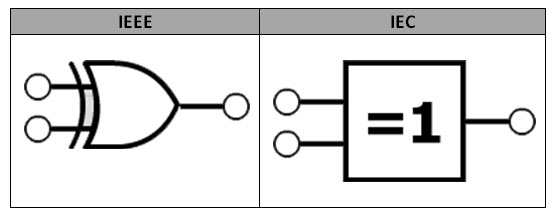

xor符号

有多种用于定义电子元件的标准。通常,我们遵循IEEE(电气和电子工程师协会)和IEC(国际电工委员会)标准。IEEE和IEC标准中的XOR逻辑符号如下所示。

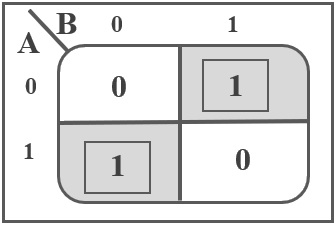

XOR门的布尔表达式不能直接像或门一样确定。由于它是混合栅极,通过乘法,添加和反相的组合给出XOR门的输出的布尔表达式。我们必须使用Karnaugh地图或K - 与真相表一起派生XOR门的布尔表达式。

xor真理表

异或门真值表如下表所示。由此,很明显,当两个输入相同时,异或门产生逻辑LOW,即在输出端逻辑' 0 '(两个输入都可以是LOW或HIGH)。

当两个输入不同时,在输出端产生一个逻辑高值,即逻辑1。

| 输入 | 输出 | |

| 一个 | B. | 问: |

| 0. | 0. | 0. |

| 0. | 1 | 1 |

| 1 | 0. | 1 |

| 1 | 1 | 0. |

XOR门的上述真理表的k映射表示如下所示。

xor boolean表达式

使用上面的真值表和相应的K-Map,我们现在可以推导出异或门的布尔表达式。如果A和B是异或门的输入,其输出为:

一个B +一个B.

异或输出表示为:

⊕B

它也可以写作:

(A + B)(一个+B.的)

应用De Morgan定律,上面的布尔表达式也可以写成:

(A + B)(a b)

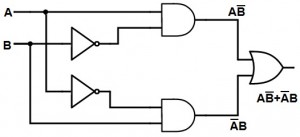

XOR门等效电路

前或门被定义为一个混合逻辑门,有两个输入来执行排他析取操作。根据以上计算,异或门的主要布尔表达式为:

一个B +一个B.

因此,具有2个输入的XOR电路使用如下所示的栅极设计。

2个输入异或门的输出只有在其中一个输入为HIGH时才为HIGH。如果两个输入相同,则输出为LOW。

使用基本逻辑门的异或门

如果一个特定的门不能直接使用,我们可以通过使用多个门来设计异或门。前或门是通用门,可以用基本逻辑门如与非门和或非门来设计。

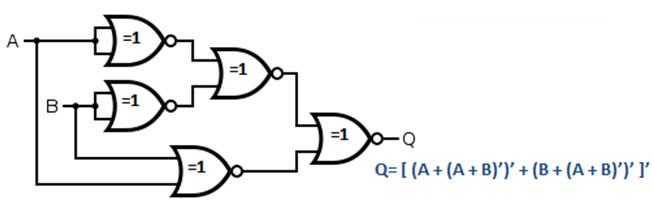

与盖茨也不

现在让我们看看如何使用NOR门来实现异或门。为此,我们必须重新编写上述XOR布尔方程式。

q =一个B +一个B.

q =一个B +一个B.+一个一个+ BB.

q =(一个+B.)(A + B)

q =(一个+B.) (a + b) = (a ' + b ') (a + b)

我们在双方接受补充:

问:=((a'+ b')(a + b))

使用De Morgan的法律,我们得到:

问:=(A'+ B')+(A + B)= (a ' + b ') ' + (a + b) '

再一次对两边进行补码,得到:

q =((a ' + b ') + (a + b) ')= (a ' + b ') ' + (a + b) ') '

此等式看起来可以使用NOR门来实现。我们需要完全五个,也不需要栅极(两个用于反转A和B,一个用于的A和B,一个用于'和B'和最终的一个,以获得上述等式)。以下图像显示使用或门实现的XOR门。

与逻辑门

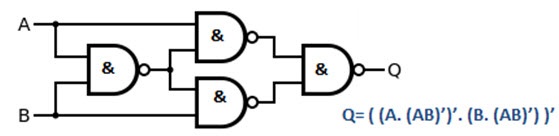

让我们现在看看我们如何使用NAND门来实现XOR门。为此,我们必须重新编写上述XOR布尔方程式。

q =一个B +一个B.

q =一个B +一个B.+一个一个+ BB.

q =(a + b)(一个+B.的)

q =(a + b)(一个+B.)=(a + b)(a'+ b')

在上述等式中,在第二个术语中应用De Morgan的法律,我们得到:

q =(a + b)(A B.的)

现在我们需要用与非门来实现这个电路。

Q = a (A B.)+ b(A B.) = a (ab) ' + b (ab) '

我们在双方接受补充:

问:= ((A B.)+ b(A B.))'=(a(ab)'+ b(ab)')

问:= ((A B.))'(b(A B.))'=(a(ab)')(b(ab)')

最后,再一次,在两边应用补码。

q =(a(a b)')'(b(a b)')'=((a(ab)')'(b(ab)')')'

这个方程看起来可以用NAND门来实现。我们完全需要我们的NAND门。下图显示了使用NAND门实现的异或门。

使用和,或和和NAND门

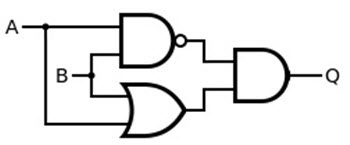

现在让我们看看如何使用NAND、AND和OR门来实现异或门。为此,我们必须重新编写上述XOR布尔方程式。

q =一个B +一个B.

q =一个B +一个B.+一个一个+ BB.

q =(a + b)(一个+B.的)

q =(a + b)(一个+B.)=(a + b)(a'+ b')

在上述等式中,在第二个术语中应用De Morgan的法律,我们得到:

q =(a + b)(A B.的)

上述等式中的第一项需要一个或门,第二项需要NAND门,并且可以使用AND栅极获得最终等式。

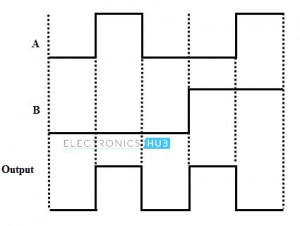

异或门的脉冲操作

2输入XOR门的脉冲操作如下所示。

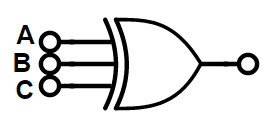

3-Input ex或门

在某些情况下,我们需要有超过2个输入的异或门。2个以上的输入异或函数称为“奇函数”或“模2和”。3输入异或门的布尔函数是:

Q = a⊕b⊕c =一个B.C +一个B.C+一个B.C+ a b c

下面给出了3输入XOR门的实际表和逻辑符号。

3输入前或门逻辑符号

3输入异或门真值表

对于三输入异或门,当奇数个输入处于高电平时,我们可以有高输入。所以3输入或门被称为“奇函数或门”。

| 输入 | 输出 | ||

| 一个 | B. | C | 问: |

| 0. | 0. | 0. | 0. |

| 0. | 0. | 1 | 1 |

| 0. | 1 | 0. | 1 |

| 0. | 1 | 1 | 0. |

| 1 | 0. | 0. | 1 |

| 1 | 0. | 1 | 0. |

| 1 | 1 | 0. | 0. |

| 1 | 1 | 1 | 1 |

常用的TTL和CMOS逻辑前或门IC

下面是一些常用的异或芯片的列表。

| IC号码 | 描述 |

| 4030 | 四输入2异或门 |

| 4070. | 四输入2异或门 |

| 7486. | 四输入2异或门 |

| 74年ls86 | 四输入2异或门 |

| 741G86. | 单2输入前或门 |

| 74136 | 带有集电极输出开路的四路2输入异或门 |

| 74386 | 四输入2异或门 |

其中,基于最受欢迎的TTL逻辑的EX-OR GATE IC是74LS86,它是四边形的XOR IC。即将到来的基于CMOS逻辑的XOR门IC,CD4030 Quad 2输入XOR IC是一个流行的选择。

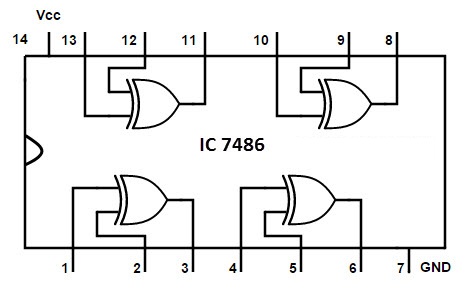

7486 Quad 2输入独家或门IC

IC 7486是Quad 2输入XOR门I.E。,它包含单个包中的四个2输入XOR栅极。IC的销图和引脚描述如下所示。

| PIN号码 | 描述 |

| 1 | 门1输入a |

| 2 | 门1输入B. |

| 3. | 门1输出y |

| 4. | 门2输入A |

| 5. | 门2输入B |

| 6. | 门2输出Y |

| 7. | 地面 |

| 8. | 输出Y |

| 9. | 门3输入a |

| 10. | 门3输入B. |

| 11. | 门4输出y |

| 12. | 门4输入A |

| 13. | 门4输入B |

| 14. | 积极供应 |

前或门的应用

许多应用中使用XOR逻辑门。其中一些如下所述。

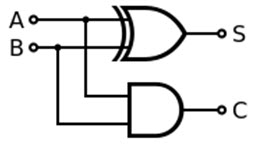

用于加法器(添加)

我们可以设计单位加法器(也称为半加倍数),这将添加两个位并产生单位输出。通过使用XOR门设计的单个比特加法器如下所示。

例如,在二进制加法中,如果我们将两位1和1相加,我们得到的答案是10,而在十进制加法中,我们得到的结果是2。半加法器的主要原理是通过异或门的输出实现尾随和,并通过与门计算进位。

我们可以将多个单位加法器电路串联成n位加法器电路,计算出较长的二进制数的和。

伪随机数生成

线性移位寄存器也称为伪随机数发生器(PNRs)。为了生成随机数,我们通过形成一个线性反馈移位寄存器来将异或逻辑门按照特定的顺序排列。

相关性和序列检测

当异或门的所有输入都是HIGH或low时,它能够产生一个低电平输入,即0。当我们在长数据序列中搜索特定的位序列时,我们使用异或门来查找所需的数据位序列。

通过计算所获得的0的数量来确定找到目标序列中所需的数据位串的准确性。在许多通信设备(如解码器和CDMA接收器)中,我们使用共同中继器,其用于在一组PRN序列中提取特定伪随机数序列的奇偶校验。

结论

独家或门(XOR门)的完整教程。您学习了XOR门的符号,真理表和布尔表达式,使用Nor和Nand Gates的实现XOR门,一个三输入XOR门,其符号,真理表和布尔表达式,一些常见和流行的XOR IC和一些XOR门的重要应用。