在本教程中,我们将学习另一种重要的触发器,即T触发器。我们将学习它的设计,工作,以及一些应用的T触发器。

介绍

T触发器也被称为“切换触发器”。以避免中间态(也称禁态)的发生SR触发器,我们应该只向触发器提供一个输入,称为触发器输入或Toggle输入(T)。

然后触发器作为一个拨动开关。切换意味着“更改下一个状态输出以补充当前状态输出”。

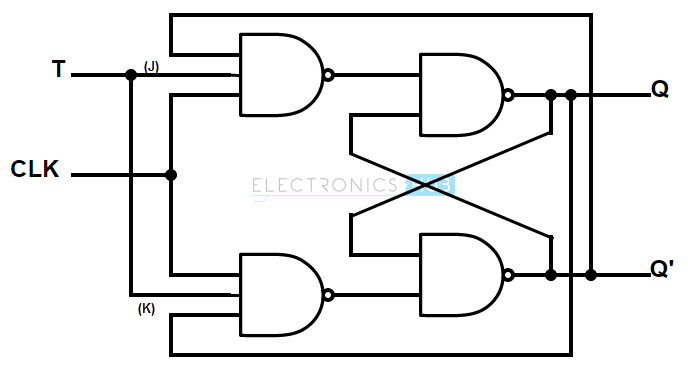

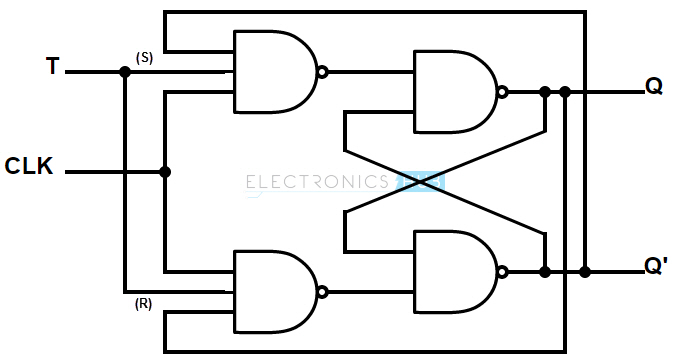

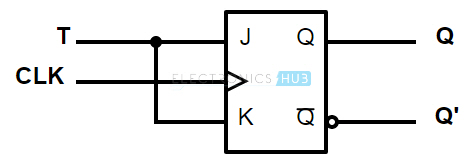

我们可以通过对触发器进行简单的修改来设计T触发器JK触发器.T触发器是一个单输入器件,因此,通过将J和K输入连接在一起,给它们一个称为T的单输入,我们可以将JK触发器转换为T触发器。

因此,T触发器有时被称为单输入JK触发器。

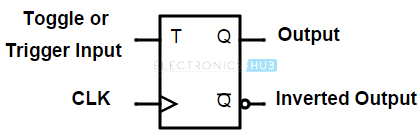

T触发器的逻辑符号如下所示。它有一个切换输入(T)和一个时钟信号输入(CLK)。

T触发器电路

我们可以用下列任何一种方法构造一个T触发器:

- 在SR触发器中连接输出反馈到输入。

- 将一个异或与T输入和Q前输出连接到D触发器的数据输入。

- 将J和K输入端硬接线在一起,并将其连接到JK触发器的T输入端。

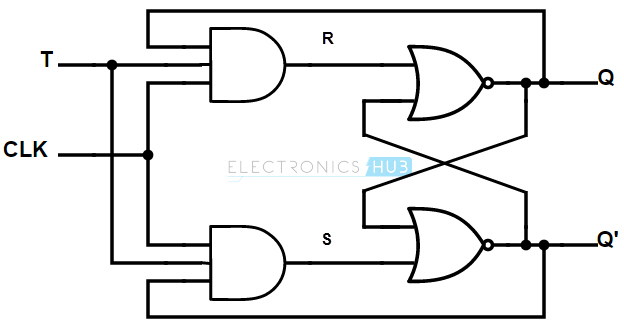

老使用触发器

我们可以通过连接和门作为输入到NOR门SR锁存器来构造一个T触发器。这些和门的一个输入是来自当前状态输出Q和它的补充的反馈问对应于相应的与门,即Q对应于与输入R和相关的与门问到与S输入相关的和门。

切换输入(T)作为输入与与门共同连接。与门也与公共时钟(CLK)信号相连。

在T触发器中,提供一串窄幅触发器作为输入(T),它会引起触发器输出状态的变化。所以,这些人字拖也被称为切换人字拖。由SR锁存器构成的T触发器的电路图如下所示。

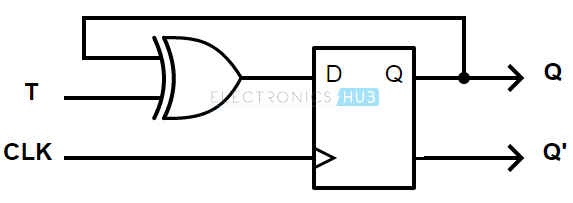

使用D触发器

类似地,可以通过修改来构造T触发器D触发器.在D触发器中,输出Q与T输入xor,并在D输入处给出。由D触发器构成的T触发器的电路如下所示。

使用JK触发器

最简单的T触发器结构是JK触发器。JK触发器的J输入端和K输入端连接在一起,并提供T输入端。由JK触发器构成的T触发器的逻辑电路如下图所示。

工作

T触发器是一种边缘触发器件,即输入时钟信号的由低到高或由高到低的过渡将引起触发器输出状态的变化。

T触发器真值表

T触发器的真值表如下所示。

| 以前的 | 下一个 | |||

| T | 问上一页 | 问上一页 | 问下一个 | 问下一个 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

如前所述,T触发器是一种边缘触发装置。例如,考虑如下所示的由NAND SR锁存器制成的T触发器。

如果输出Q = 0,则上NAND (NAND C)门处于disable状态(没有任何支配输入),下NAND (NAND D)门处于enable状态(Q反馈为支配输入)。这意味着,Toggle Input将为RS触发器,R= 1,年代= 0。如果你还记得真值表RS触发器,此条件将设置输出。因此,Q等于1。

如果输出Q = 1,则上与非门为enable,下与非门为disable。这允许Toggle Input设置RS触发器,R= 0和年代= 1。这将使触发器复位,即Q = 0。

简单来说,T触发器的操作是

当T输入为LOW时,T触发器的下一个状态与当前状态相同。

- T = 0,现在状态= 0,然后下一个状态= 0

- T = 0,当前状态= 1,然后下一个状态= 1

当T输入为高时,在时钟信号正过渡期间,T触发器的下一个状态是当前状态的补充。

- T = 1,当前状态= 0,然后下一个状态= 1

- T = 1,当前状态= 1,然后下一个状态= 0

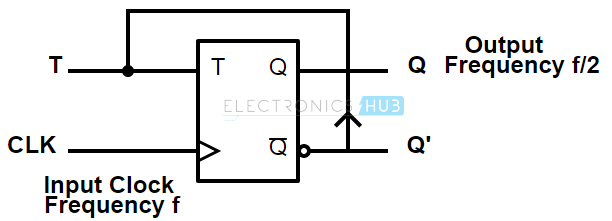

由于每个进入触发器交替改变SET和RESET输入,触发器切换。因此,要完成一个完整的波形输出周期,需要两个触发器。这意味着T触发器产生的输出频率正好是输入频率的一半。因此,一个T型触发器将充当“分频电路”。

T触发器的主要缺点是,在一个应用的触发脉冲上,触发器的状态只有在前一个状态已知时才能知道。

一般来说,T型触发器不能作为集成电路使用。因此,可以用JK触发器、SR触发器和D触发器来构造它们。由JK触发器制成的T触发器的符号如下图所示。

应用程序

现在让我们来看看T触发器的几个重要应用。

- 分频电路

- 2位并行负载寄存器

分频电路

通过将互补输出Q '反馈到T输入端,T触发器可以用作“分频电路”。使用T触发器的分频器的逻辑符号如下所示。

使用T触发器的2位并行加载寄存器

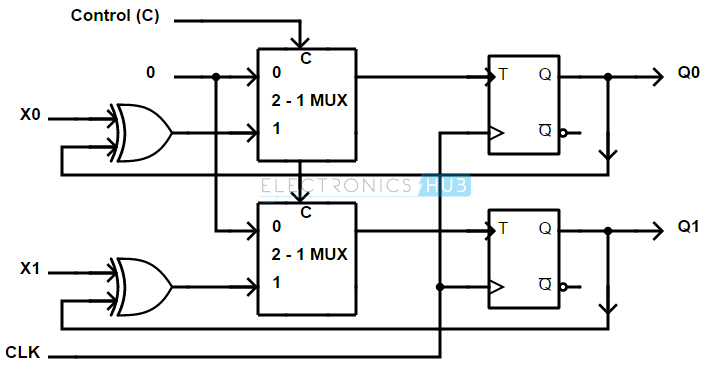

我们使用寄存器和移位寄存器来存储数据。但是大小总是内存元素(如寄存器)的主要关注点。因此,我们使用2位并行加载寄存器代替4位寄存器。

在设计并行加载寄存器时,需要考虑两个操作:

- 保存的数据

- 并行加载数据

为了保持T触发器的输出,输入T应该是0。但平行负载是一个困难的部分。

并行加载是指在触发器的输出端得到X的值。为了做到这一点,我们将X输入异或,并将状态输出给2到1 MUX。MUX的另一个输入是一个常数0(逻辑低)。MUX的输出端连接到T触发器的输入端。

因为它是一个2位寄存器,所以需要两个这样的组合。一个2位并行负载寄存器的电路如下所示。

结论

一个简单的初学者教程,关于T触发器,也被称为切换触发器。您学习了如何使用其他触发器如SR触发器,JK触发器和D触发器设计一个T触发器,Toggle触发器的工作原理,T触发器的真值表,以及一些有用的应用程序。