在本教程中,我们将简要介绍逻辑门。我们将在TTL电路,CMOS电路,一些简单的逻辑门(例如或不,NON,NAND和等)中看到不同的逻辑级别。

逻辑门简介

逻辑门是数字电子设备的核心。门是一种电子设备,用于在两个值信号上计算功能。逻辑门是数字电路的基本构建基础。

基本上,所有逻辑门都有一个输出和两个输入。某些逻辑门(例如不门或逆变器)只有一个输入和一个输出。逻辑门的输入旨在通过接收电压输入来仅接收二进制数据(仅低0或高1)。

低逻辑水平代表零电压,高逻辑水平代表3或5伏的阳性电源电压。

我们可以连接任意数量的逻辑门来设计所需的数字电路。实际上,我们在IC中实施了大量逻辑门,通过它们可以节省大量逻辑门所占据的物理空间。我们还可以使用集成电路(IC)以高速进行复杂的操作。

通过结合逻辑门,我们可以设计许多特定的电路,例如触发器,闩锁,多路复用器,换档寄存器等。

数字逻辑水平

逻辑水平定义为信号的特定状态或电压。我们知道0和1是逻辑门的两个状态。逻辑水平0和1分别称为低和高。在数字电子学中,这些二元逻辑水平在数据存储,数据传输中起着至关重要的作用。

通常,这些逻辑水平可以像在状态下和关闭状态一样理解。正如我们之前所说,逻辑水平通过电源电压引入逻辑门。如果逻辑门的电源电压为0伏,则指逻辑水平低或状态下。

同样,如果对逻辑门的电源电压为5伏或3.3伏(对于现代IC),则是指较高的逻辑水平或状态。在设计ICS时,制造商将遵循TTL或晶体管 - 晶体管逻辑作为标准电压水平。

什么是活跃的高和活跃的低点?

我们看到IC和微控制器中的主动高输入和活跃的低输入引脚。你知道它们的真正含义吗?他们只是描述了我们如何激活销钉。

这意味着活跃的低引脚必须连接到低逻辑水平或地面。以同样的方式,活跃的高引脚必须连接到高逻辑水平或5伏或3.3伏。

让我们以一种简单的方式理解这一点。当我们在移位寄存器IC中看到启用引脚CE,而没有任何线(bar),我们将其连接到主动低输入,即接地0伏。否则,如果我们将其在(CE)̅上线上的启用引脚看到,则将其连接到活动的高输入,即到3.3或5伏电源,以启用引脚。

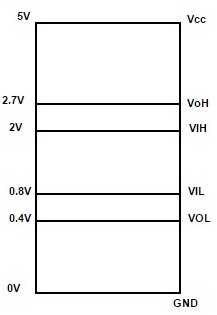

TTL逻辑级别

TTL逻辑级别是大多数逻辑设备的标准逻辑级别。TTL表示晶体管 - 晶体管逻辑。晶体管是电控制开关。逻辑家庭的电压水平是

voh - 最小。高信号的输出电压水平

卷 - 最大。低信号的输出电压水平

VIH - 最小。要考虑高信号的设备的输入电压水平

VIL - 最大。要考虑低信号的设备的输入电压水平

如果我们观察到TTL逻辑水平,我们可以观察到输出的最小高压水平为2.7伏。这意味着,当设备驾驶高时,电压应至少为2.7伏。

同样,输入的最小高压水平为2伏。因此,将大于2伏的电压视为逻辑1,归功于TTL设备。0.8伏和2伏之间的电压称为噪声边缘。

以同样的方式,输出的最大低压水平为0.4伏。这意味着,当设备驾驶高时,电压应小于0.4伏。同样,输入的最大低压水平为0.8伏。

因此,小于0伏的电压将以逻辑0视为ttl设备。因此,当向逻辑设备提供0.8 V和2 V之间的电压时,设备的逻辑水平将在高和低之间发生变化。这种情况称为“浮动”。

TTL设备的输入和输出公差的另一个过程是

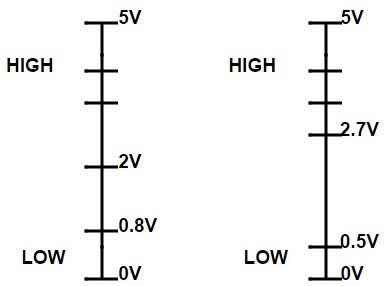

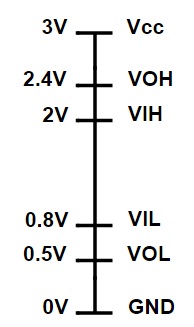

CMOS逻辑级别

CMOS逻辑设备也被称为3.3伏设备,因为CMOS设备的最大电压水平为3.3V。这是一种先进的技术,它将在低电源(3.3 V而不是5 V)上运行设备。

通常,我们使用5V设备(TTL兼容)来设计逻辑门,因此这些CMOS设备用于与TTL设备接口。CMOS设备可以与任何TTL设备接口,并且不需要任何其他组件。

例如,CMOS设备的高逻辑级别(1)的最小值为2.4V。因此,可以使用TTL设备解释该设备,该设备的逻辑(v -ih)1的最小输入电压为2V。

但是,在将TTL连接到CMOS设备(3.3 V和5 V)之前,我们需要检查3.3 V设备是否耐受5 V。因为当我们提供高于3.6 V的电压时,许多将永久造成芯片损坏。我们可以使用电压分离器电路或逻辑水平变速器来控制5 V电压信号。

噪音余量

逻辑水平的噪声边缘定义为高输入(VIL最大)最大低压和逻辑门低输入(VIL min)的最大电压之间的电压差距。噪声边缘还定义为电压信号超过精确高或精确的阈值水平的量。

让我们清楚地理解这一点。当逻辑电路在0伏和1.2伏之间发生变化时,任何低于0.2伏特的电压都被认为是低的,即0.0。

CMOS逻辑设备比TTL逻辑设备具有更高的噪声水平或噪声率,因为它们的高逻辑(VOH Min)的最小输出电压更接近电源电压,低逻辑(VOL MAX)的最大输出电压接近0。因此,噪声水平是逻辑电路可以承受的最大噪声。

如果我们应用某些噪声水平的电压,我们不确定该电路是否会响应。噪声水平是由外部干扰(例如电源电压波动和电路中的其他导体)引起的不良电压水平。

电路可以忍受的噪声水平称为“噪声免疫”或“噪声余量”。对于TTL设备,输出电压的公差范围高于输入电压。

简单二极管逻辑门

二极管可以像开关一样起作用,因此它们用于数字逻辑操作和开关。对于低阻抗和高阻抗状态,二极管将在正向偏置和反向偏置方面起作用。

二极管仅会在一个方向(正向偏置)上进行,并且在反向偏置条件下保持关闭。因此,它的行为就像开关。现在,让我们看看一些简单的二极管逻辑门,这些门仅使用二极管和电阻器来构建。

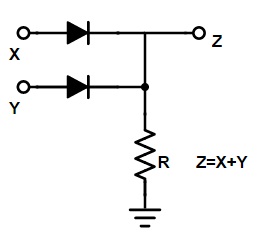

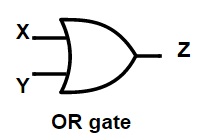

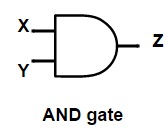

或门

下图显示了由两个二极管设计的简单或门。两个二极管给出了该电路的输入。在此,逻辑高(1)由+5伏表示,逻辑低(0)由0伏或接地表示。

在下面的电路中,两个输入是未连接的,因此输出为0,即逻辑低。

如果两个输入中的任何一个连接到+5伏,则二极管会向前偏置,并将进行。因此,输出为逻辑高,即1。

如果将+5 V的电压连接到两个输入(两个二极管),则它们将处于正向偏置状态,这使得以高逻辑设置的输出或电路。

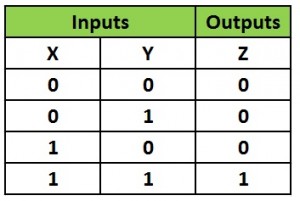

在数学上以z = x + y给出了门的功能,其中z是或x的输出,x,y是输入。逻辑或门的真实表和逻辑图和电路图如下所示。

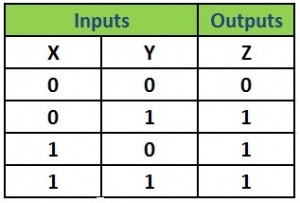

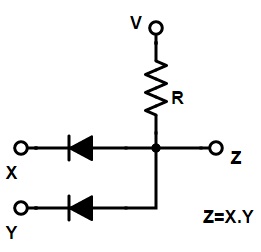

和门

下图显示了由两个二极管设计的简单和门。在此过程中,电路驱动电压V通过电阻连接到两个偏线连接的二极管,R。R。由两个二极管给出该电路的输入。

在此,逻辑高(1)由+5伏表示,逻辑低(0)由0伏或接地表示。

在下电路中,两个输入没有连接,因此输出也为0,即逻辑低。

如果两个输入中的任何一个连接到+0伏特,则二极管将变为反向偏置,并且不会进行并使输出作为低逻辑,即0。

如果将+5 V的电压连接到两个输入(两个二极管),则两个二极管将处于正向偏置状态,这使得和电路的输出和电路设置为高逻辑。

在数学上以z = X. y给出了栅极和门的功能,其中z是输入和x,y是输入。逻辑和门的真实表和逻辑图和电路图如下所示。

和逻辑电路逻辑符号真相表

晶体管逻辑门

像二极管一样,晶体管也充当电子开关。我们也可以使用晶体管设计逻辑门。让我们看看晶体管制作的逻辑门。

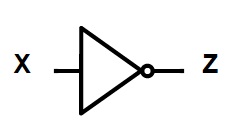

不是门

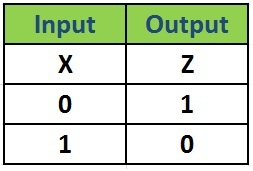

非门通常被称为逆变器。它产生确切的反向输出到给定输入的输出。它只有一个输入和一个输出。不栅极的输出始终是其输入的补充。当低输入信号连接到非门的输入时,输出将为高(逻辑1)。

同样,如果将高输入信号连接到输入,则输出将为较低(逻辑0)。非操作用“ - ”栏符号表示。如果未门的输入为x,并且输出为z,则将不栅极的操作作为z = x̅,如x bar所说。

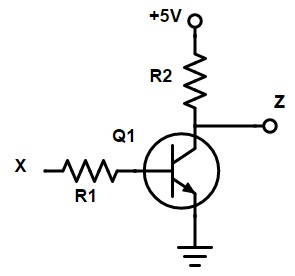

下面显示了使用晶体管设计的非门。输入通过电阻给晶体管的底部。该晶体管电路由+5伏电压驱动。

当输入连接到低级信号0 V时,晶体管将反向偏置。因此,任何电流都不会流过它,因此它保持不变。由于没有流过晶体管的电流流,因此电阻不存在电压降。因此,输出将对应于使输出逻辑高的+5伏对应。

但是,如果连接到输入的+5 V,则输出电压将变为0。

还有两个可以通过使用晶体管设计的门,它们是NAND门,也不是门。这些大门称为“通用大门”。

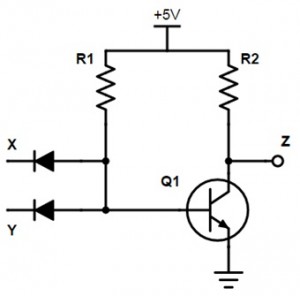

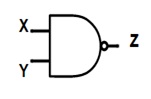

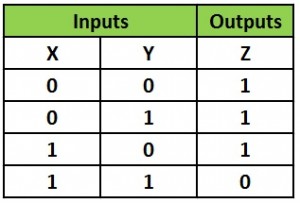

NAND大门

NAND门具有执行3个操作,例如和或不可能的能力。这扇门是Not&and Gates的组合。NAND门输出等于和门的倒数。

NAND门具有两个输入X和Y,并且一个输出Z。输入应用于连接到晶体管的二极管。NAND门电路由+5伏驱动。

当两个输入连接到5 V的电压电源时,二极管D1和D2都处于OFF状态。然后,晶体管Q1能够通过电阻从电源电压驱动。因此,晶体管处于状态,输出电压VCE(SAT)变为0。

同样,当应用低电平电压到输入即0 V时,晶体管将关闭,输出电压变为+5V。数学上表示为z =(x.y)̅。

因此,仅当两个输入都高时,NAND门的输出才会变得较低。对于任何其他输入组合,它变得很高。NAND门的真实表,逻辑符号和晶体管电路图如下所示。

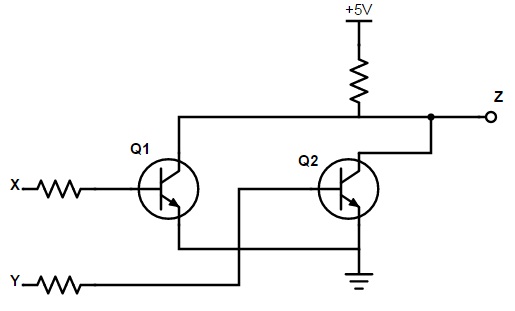

也不是门

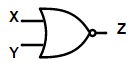

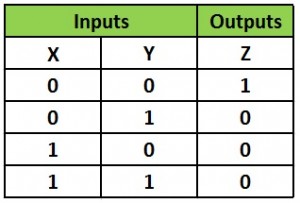

门不是门和或门的组合。NOR门输出等于或门的倒数。Nor Gate具有两个输入X和Y,以及一个输出Z。

设计的晶体管也不具有两个N-P-N晶体管,带有电压电源或+5伏。

当Nor Gate的两个输入连接到0伏时,晶体管Q1和Q2处于OFF状态。因此,没有电流流过电阻,并且电阻越过电压降。然后,输出电压等于电源电压+5伏,即高逻辑水平。

如果输入中的任何一个连接到+5 V,则晶体管将处于状态。因此,电压降将很高。因此,电路的输出电压为0 v,即等于接地电压。

在数学上,门被表示为z =(x+y)̅。

因此,仅当两个输入均低时,NAND门的输出才变高。对于任何其他输入组合,它变得较低。NOR门的真实表,逻辑符号和晶体管电路图如下所示。

74系列逻辑IC

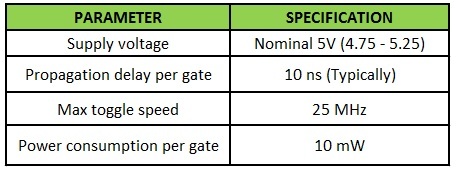

7400系列IC在1960年代左右引入。尽管正在使用许多其他用于逻辑门的IC,但由于其简单的编号方案和标准,7400 TTL系列IC已变得最受欢迎。下面给出了一些规格和主要功能。

74系列IC是通过使用双极晶体管技术制造的,因此它们被称为TTL家族IC。(TTL表示晶体管 - 透射逻辑)。7400 IC将在+5伏特的供应方面工作,这成为多年来逻辑电路的标准电压水平,直到CMOS技术的发展。

这些是用于逻辑电路设计的广泛使用的IC系列。在这个7400系列IC的早期,我们有TTL系列芯片。摩托罗拉公司(Motorola Company)开设了一个名称为mttl的逻辑家庭,这意味着摩托罗拉晶体管横向横幅逻辑。

其他研究人员和制造商也推出了其他一些ICS,例如,签名,Fairchild和国家半导体。

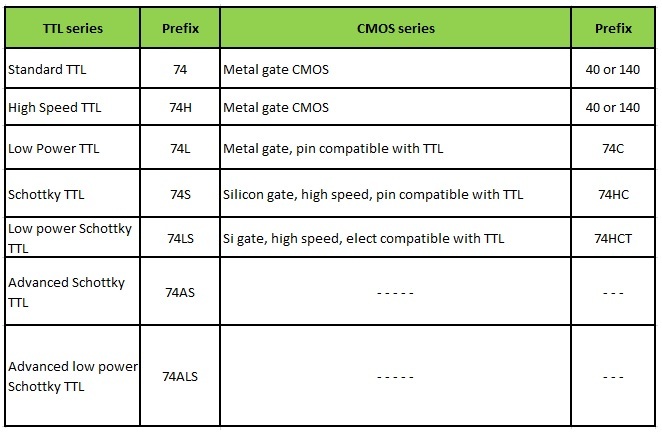

有几个IC系列编号为74xx00。XX代替的字母将指示IC类型和规格。IC系列的不同类型是74LS00、74HC00和74HCT00等。让我们看看每个IC系列的规格和目的。

74LS系列

这是使用TTL电路的低功率Schottky家族。这些在操作中很快,但比其他逻辑家庭消耗更多的功率。

74HC系列

该系列是高速CMOS家族。这些IC具有4000系列的低功率特征和74LS系列速度的组合。

74HCT系列

这是74HC家族的非常特殊的版本。它具有74LS TTL兼容输入。因此,它可以很容易地与74LS系列连接。74HCT家族被用作74LS系列的替代,因为它们是低功率要求。

74HCT系列的缺点是它们对噪声的免疫力较小,即噪声耐受性较小。

74HC系列中使用的CMOS电路和74HCT系列的静态灵敏度。这意味着,如果我们在充电时触摸IC的任何销钉,它将损坏IC。

下面列出了TTL和CMOS家族的前缀。

下面给出了一些用于逻辑门设计的最常用的IC

Quad 2输入门

- 74LS00 - Quad 2输入NAND大门

- 74LS01 - Quad 2输入NAND大门,开放收集器输出

- 74LS02 - Quad 2输入或门

- 74LS03 - Quad 2输入NAND GATE带有开放收集器输出

- 74LS08 - 四边形2输入和门

- 74LS09 - Quad 2输入和带开放收集器输出的门

- 74LS32 - Quad 2输入或门

- 74LS132 - Quad 2输入NAND GATE带有Schmitt触发输入

- 74LS37,74LS32,74LS28 - 四Quad 2输入或门

- 74LS26 - Quad 2输入NAND GATE,OC(15V)

- 74LS28 - Quad 2输入NAND GATE带有OC(15V)

- 74LS33 - Quad 2输入或大门,开放收集器输出

- 74LS38 - Quad 2输入或大门,开放收集器输出

- 74LS38 - Quad 2输入NAND大门,开放收集器输出

三重3输入门

- 74 LS 10 - 三重3输入NAND

- 74 LS 11 - 三重3输入和

- 74 LS 12 - 带有开放收集器输出的三重3输入NAND

- 74 LS 27 - 三重3输入

- 74LS15 - 三重3输入和大门,开放收集器输出

双4输入门

- 74LS13 - 双4输入NAND施密特触发器

- 74 LS 20 - 双4输入NAND

- 74 LS 21 - 双4输入和开放收集器输出

- 74LS22 - 双4输入NAND大门,开放收集器输出

- 74LS40 - 双4输入NAND门

- 74LS30 - 8输入NAND门

十六进制不是大门

- 74 LS 04 - 十六进制

- 74 LS 05 - 十六进制不带开放式收集器输出

- 74 LS 14 - 十六进制不带Schmitt触发输入

- 74LS19 - Nand Schmitt触发器,图腾杆输出

- 74LS23 - 2x四输入或频闪

- 74LS25 - 2x四输入或频闪

- 74LS30 - 8输入NAND大门

- 74LS39 - 4X两个输入NAND,开放收集器