简介

D触发器也被称为“延迟触发器”或“数据触发器”。它们用于存储1位二进制数据。它们是数字电子中应用最广泛的触发器之一。D触发器除了作为数字系统的基本存储元件外,还被认为是延迟线元件和零阶保持元件。

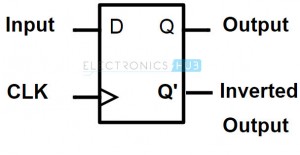

D触发器有两个输入,一个时钟(CLK)输入和一个数据(D)输入和两个输出;一个是用Q表示的主输出,另一个是用Q '表示的Q的补码。D触发器的符号如下所示。

建设

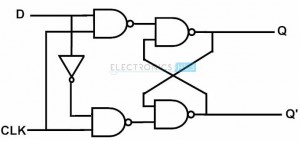

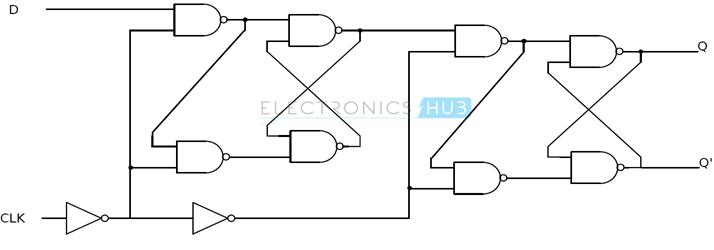

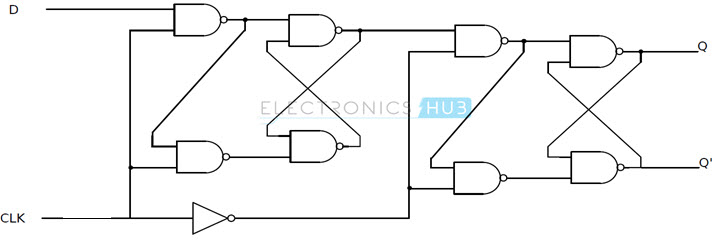

通过对SR触发器进行修改,构造出D触发器。S输入是D输入R输入是反D输入。因此,D触发器类似于SR触发器,两个输入是互补的,因此不会有任何中间状态发生的机会。SR触发器的主要缺点是消除了D触发器的争用条件(由于输入是反向的)。D型触发器的电路图如下图所示。

工作

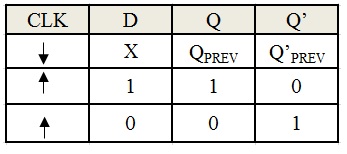

当我们不应用任何时钟输入到D触发器或在时钟信号下降沿期间,输出将没有变化。它会在输出q处保持之前的值。如果时钟信号高(更准确地说是上升边缘),如果D输入高,那么输出也高,如果D输入低,那么输出也会变低。因此,在存在时钟信号的情况下,输出Q跟随输入D。

简单来说,对于时钟信号的正跃迁,

如果D = 0 => Q = 0,则复位触发器。

如果D = 1 => Q = 1,则设置触发器。

注意:↑“↓”表示时钟正向边缘,“↓”表示时钟负向边缘。

Edge触发D触发器

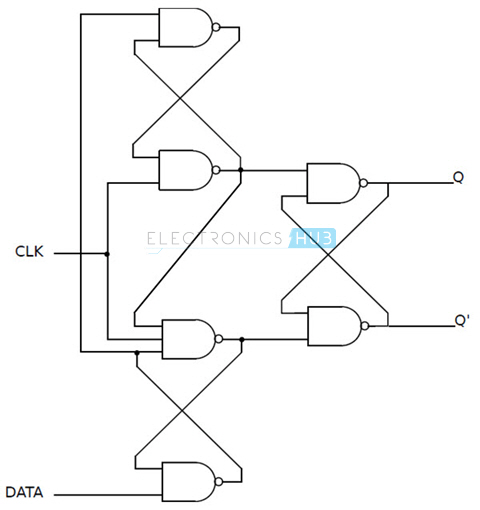

正向边缘触发的D触发器由三个SR NAND锁存器构成。输入级由两个锁存器组成,输出级由一个锁存器组成。在输入阶段,数据输入连接到其中一个NAND锁存器,时钟信号(CLK)并联连接到两个SR锁存器。

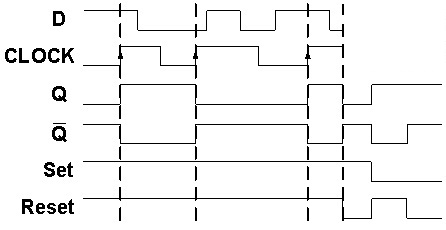

操作可以这样解释,当时钟信号低时,输入级的输出是高逻辑,而不考虑输入数据的值。因此,它存储了以前的数据。当时钟经过正转换(由低到高)时,输入级的输出负责最终输出的设置或复位操作,并依赖于数据信号。如果数据输入高,上锁存器的输出变低,从而设置锁存器输出为1,如果数据输入低,下锁存器的输出变低,将输出复位为0。如果多个数据信号的时钟持续高,只考虑第一个数据输入,而通过强制输出锁存器到其之前的状态,忽略其余的数据输入,因为只要时钟信号高,低输入是活跃的。因此,外部锁存器仅在时钟处于低逻辑状态时存储数据。触发D触发器的主要作用是保持输出,直到时钟脉冲由低到高变化。边缘触发D触发器的时序图如下所示。

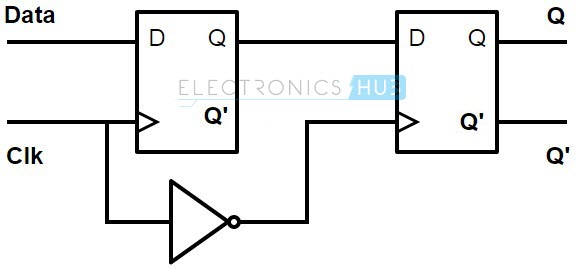

Master Slave D触发器

主从D触发器的设计方法是将两个门控D锁存器串联起来,并将一个反向的使能输入连接到两个锁存器中的任意一个。只有主闩的改变才会带来从闩的改变。这些被称为主从触发器。根据不同的设计,主从触发器的总电路可以在时钟信号上升沿触发,也可以在时钟信号下降沿触发。

主从D触发器的符号表示,它响应时钟在其下降沿,如下所示。

主从D触发器如下所示是一个正边缘触发设备,这意味着它将在时钟输入有上升边缘时工作。第一个触发器(主触发器)与负时钟信号相连,即反向时钟信号;第二个触发器(从触发器)与双逆时钟信号相连,即正常时钟信号。

操作

正边触发的主从D触发器的操作解释如下。

- 如果时钟低,则主控触发器的使能信号高。当时钟信号由低到高变化时,主触发器存储D输入的数据。同时在第二个触发器,由于双重反转,使能信号随时钟信号由低到高。在上升沿期间,主触发器锁定的数据被传递给从触发器。

- 当时钟信号从高到低时,从触发器将接收到主触发器的输出作为输入,改变其状态。主控触发器将接受下一个上升沿输入的最新值。

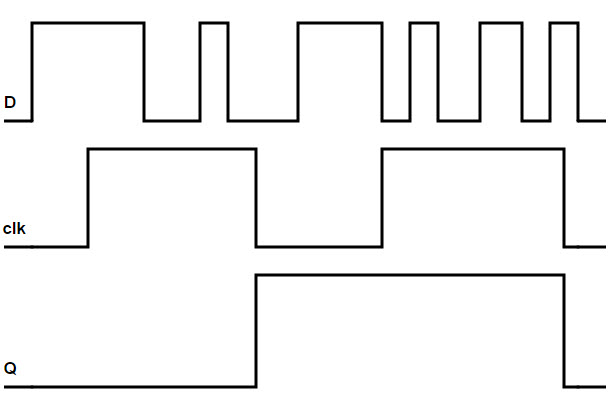

主从D触发器时序图如下图所示。

一个简单的修改将把上面的装置变成负边触发装置。通过沿时钟信号路径消除第一逆变器形成负边缘触发的主从D触发器。

应用程序

D型人字拖是使用最广泛的人字拖之一。D触发器的一些应用是

- 数据存储寄存器。

- 作为移位寄存器的数据传输。

- 分频电路。

数据存储

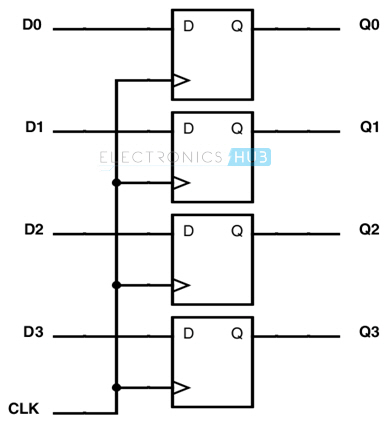

在数字电路中,数据通常以一组比特的形式存储,用数字和代码表示。因此,很容易在平行线上获取数据,并同时将数据存储在一组按特定顺序排列的触发器中。寄存器是基本的多位数据设备。它们是通过连接多个D触发器而形成的,这样就可以存储多个位的数据。

每个D触发器与各自的数据输入相连接。所有触发器的时钟输入是相同的,因此当施加正边缘触发的时钟信号时,所有触发器将同时存储各自D输入的数据。

数据传输

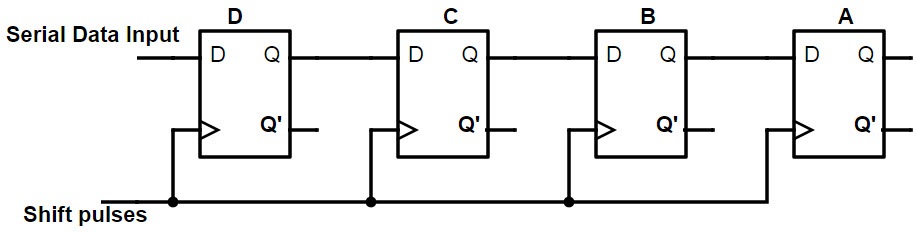

D型触发器也广泛应用于数据传输。为了传输数据,连接D个触发器形成移位寄存器。具有相同时钟信号的D触发器级联将形成移位寄存器。移位寄存器可以在不改变位序列的情况下移位数据。当一个时钟脉冲被应用时,一位数据被转移或转移。移位寄存器可以临时存储数据。

使用D触发器的4位存储移位寄存器如下所示。

移位寄存器用于串行到并行和并行到串行的数据转换。它们也被用作脉冲扩展器和延迟电路。

频率分割使用D触发器

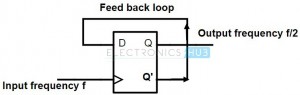

采用D型触发器开发了分频电路。这是D Flip Flop最重要的应用。在频分电路中,D触发器的状态输出(Q’)连接到数据输入(D)作为一个闭环反馈回路。两个连续的公鸡脉冲将使触发器切换到Toggle,每两个时钟周期。

顾名思义,分频电路用于产生恰好是输入频率一半的数字信号输出。在电路设计中,一般采用分频电路异步计数器.

电路的操作非常简单。输入数据信号由时钟输入信号进行计时。该电路将通过使用反馈回路进行输入频率的分割,即连接到从Q '输入的数据。分频电路每两个时钟脉冲将输入频率除以2。

这可以用输出与时钟信号的比较来解释。

在一种情况下,当Q输出为1,Q '输出为0,那么来自D输入的数据通过时钟输入信号的下一个正走向边缘的Q输出进行计时。在这种情况下,输出从高变为低。这里的输出保持不变,直到出现下一个正时钟信号。同样,Q '输出也是计时的。由于时钟输入再次为1,这将改变触发器的输出状态。

我们可以观察到,分频电路的输出只随输入时钟信号的正行边缘而变化。我们知道每条正边在一个完整的时钟周期中出现一次。因此,根据时钟的正边缘D触发器将输入脉冲减半,即将时钟脉冲除以2。