在本教程中,我们将学习顺序电路,什么是顺序逻辑,顺序电路与组合电路有什么不同,不同类型的顺序电路,一些重要的顺序电路基础知识和更多。

组合逻辑和顺序逻辑是数字系统设计的基本组成部分。组合电路包括多路复用器、解多路复用器、编码器、解码器等,而顺序电路包括锁存器、触发器、计数器、寄存器等。

要了解更多关于顺序逻辑和它的所有元素,如时钟,触发,同步,异步电路等的基础知识,请继续阅读下面的教程。

简介

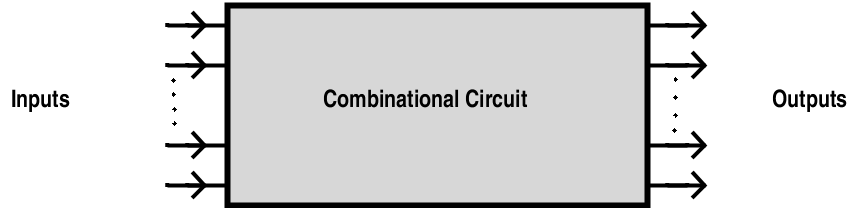

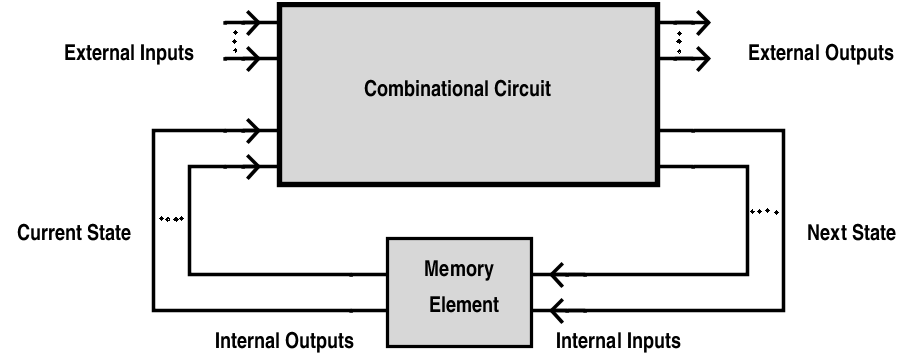

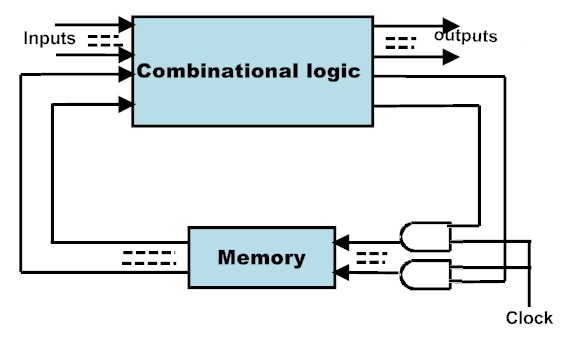

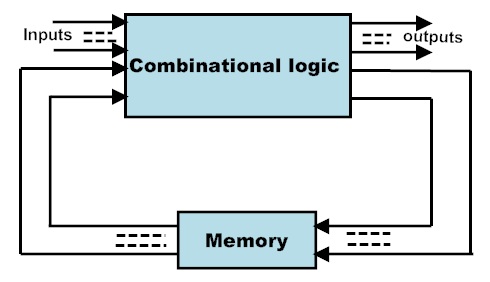

顺序逻辑电路的输出不仅依赖于输入信号的当前值,而且还依赖于输入信号的前一个值(值的历史),这与组合电路相反,组合电路的输出只依赖于任何时刻的输入信号的当前值。顺序电路可以看作是带有反馈电路的组合电路。顺序电路使用触发器之类的存储元件作为反馈电路来存储过去的值。顺序逻辑的框图如下所示。

序列逻辑电路用于构造有限状态机,有限状态机是所有数字电路和存储电路的基本组成部分。基本上,实际数字设备中的所有电路都是组合逻辑电路和顺序逻辑电路的混合体。

例子:

一般来说,我们在日常生活中会遇到很多计数器来计算物体的数量。例如,计数进出礼堂的观众人数,计数停车的车辆数量。在这种情况下,当任何人进入礼堂时,计数器根据其现值增加其价值。类似地,它会根据之前和现在的价值递减。因此Counter保留计数器的当前状态以执行下一个操作。

这类似于顺序电路,根据之前和现在的信号改变其状态。

组合电路与顺序电路

|

|

|

|---|---|

| 产出只取决于投入的现值。 | 输出取决于输入的当前和以前的状态值 |

| 当输出随输入值的变化而变化时,这些电路不会有任何存储器。 | 顺序电路有某种存储器,当它们的输出根据前值和当前值发生变化时。 |

| 不涉及任何反馈。 | 在顺序电路中,输出作为反馈路径连接到它。 |

| 用于基本布尔运算。 | 用于记忆装置的设计。 |

| 实现在:半加法器电路,全加法器电路,多路复用器,解复用器,解码器和编码器。 | 实现在:RAM,寄存器,计数器和其他状态保持机。 |

C在顺序电路中锁定信号

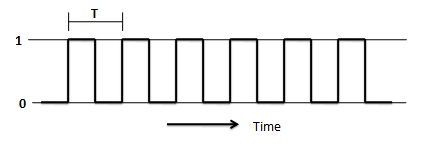

时钟信号在时序电路中起着至关重要的作用。时钟是一个信号,它在逻辑电平0和逻辑电平1之间反复振荡。恒频方波是最常见的时钟信号形式。时钟信号有“边缘”。这些是时钟从0到1(正边)或从1到0(负边)的瞬间。

时钟信号控制时序电路的输出,它决定了记忆元件何时以及如何改变它们的输出。如果时序电路没有任何时钟信号作为输入,电路的输出就会随机变化。这样它们就不能保持它们的状态直到下一个输入信号到达。而具有时钟输入的时序电路,在下一个时钟边缘出现之前,将保持其状态。

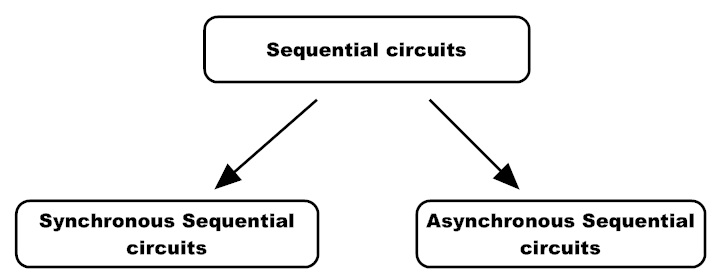

顺序电路的分类

按时钟信号输入的不同,时序电路分为两类。

- 同步时序电路

- 异步时序电路

同步时序电路

定义:

在同步时序电路中,输出依赖于在时钟实例中输入的当前和以前的状态。电路使用存储器元件来存储前一状态。这些电路中的存储元件将具有时钟。所有这些时钟信号都是由同一个时钟信号驱动的。

- 使用时钟信号,所有存储单元的状态都会发生变化。

- 与异步电路相比,这些电路稍微慢一些,因为它们等待下一个时钟脉冲到达来执行下一个操作。

- 这些电路可以被计时或脉冲。

- 在输入端使用时钟脉冲的同步顺序电路称为时钟顺序电路。它们非常稳定。

- 利用脉冲改变其状态的顺序电路称为脉冲顺序电路或无时钟顺序电路。

我们在哪里使用同步顺序电路??

•用于MOORE-MEALY状态管理机的设计。

•它们用于同步计数器、触发器等。

同步时序电路的局限性

- 在同步时序电路中,所有的触发器都必须连接到时钟信号。时钟信号是非常高频的信号,时钟分布消耗和耗散大量的热量。

- 关键路径或最慢路径决定了最大可能的时钟频率。因此它们比异步电路慢。

异步时序电路

定义

不依靠时钟信号工作的顺序电路称为“异步顺序电路”。

- 当输入信号发生变化时,这些电路会立即改变它们的状态。

- 电路的行为是由任何时刻的信号和输入信号的变化顺序决定的。

- 它们不工作在脉冲模式。

- 它们有更好的性能,但由于时间问题,很难设计。

- 当我们需要低功耗操作时,我们通常使用异步电路。

- 它们比同步顺序电路更快,因为它们不需要等待任何时钟信号。

我们在哪里使用异步顺序电路??

当操作速度很重要时,就使用这些工具。由于它们独立于内部时钟脉冲,所以运行速度很快。因此可用于快速响应电路中。

- 用于具有各自独立时钟的两个单元之间的通信。

- 当需要更好的外部输入处理时使用。

异步时序电路的局限性

- 异步时序电路的设计难度较大。

- 虽然它们的性能更快,但它们的输出是不确定的。

序贯电路中的反馈

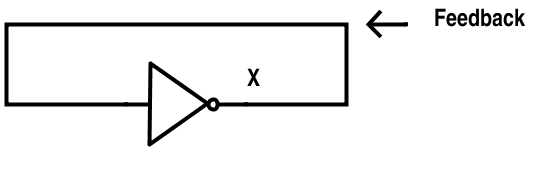

组合电路不需要任何反馈,因为输出完全依赖于输入的当前值。但在顺序电路中,输出依赖于输入的过去值和当前值。为了使存储器元件像触发器一样,必须在电路中引入反馈。例如,考虑一个简单的反馈电路,如下所示。

我在一个实例中,f0是逆变器的输入,这个0会传播,输出是1。这个1作为输入反馈回来。这个1会传播,输出是0。这个过程重复,结果是输出在0到1之间的连续振荡。在这种情况下没有稳定状态。

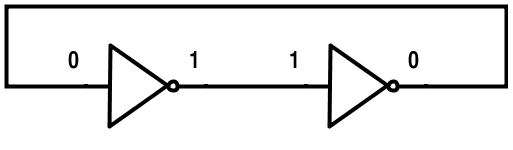

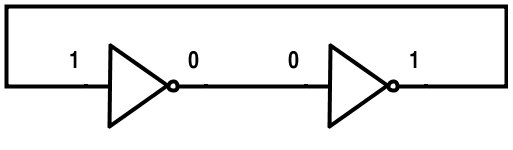

现在考虑如下两个逆变器连接的例子。

这里两个逆变器背对背连接,第二逆变器的输出反馈到第一逆变器的输入。如果0是第一个逆变器在某实例的输入,它通过第一个逆变器传播,输出为1。这个1输入到第二个逆变器,并通过它传播。第二逆变器的输出为0,该输出反馈给第一逆变器。但是第一个逆变器的输入已经为0,因此没有变化。该电路称为稳定电路。当第一个逆变器的输入为1时,可以获得另一个稳定状态。

门闩和人字拖

门闩

锁存器是时序电路中一个基本的构建元件。锁存器没有任何时钟信号,即它们是异步时序电路。

•门闩由静态门组成。

锁存器是一种双稳态多谐振荡器,即它有两种稳定状态,并可以在这些状态之间切换。

闩锁将有一个反馈路径从输出。因此,它们可以利用输入信号的前一和当前状态随时改变输出。

•当使能时,锁存器的输出受其输入的连续影响,即当输入改变时,输出立即改变。当禁用时,锁存器的状态保持不变,即它会记住它之前的值。时钟或使能信号被用作控制信号。

•闩锁不断检查所有的输入,并相应地改变其输出时启用。

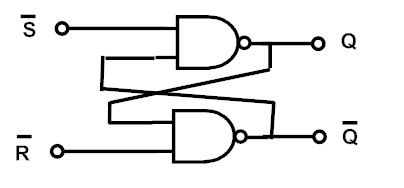

示例:S-R闩锁是简单闩锁的一个例子。

示例:S-R闩锁是简单闩锁的一个例子。

触发器

触发器也是同步时序电路的一个组成部分。它有两种稳定状态。它可以存储一位信息。触发器将有一个时钟信号。它们的状态随时钟脉冲的变化而变化。这些器件将有两个状态和一个反馈路径。

- Flip-Flop是边缘敏感的。当时钟信号发生由低到高或由高到低的转换时,它们的状态就会发生变化。

- 时钟信号从0到1或从1到0转换后,即时钟为恒定的0或1时,即使输入改变,状态也保持不变。

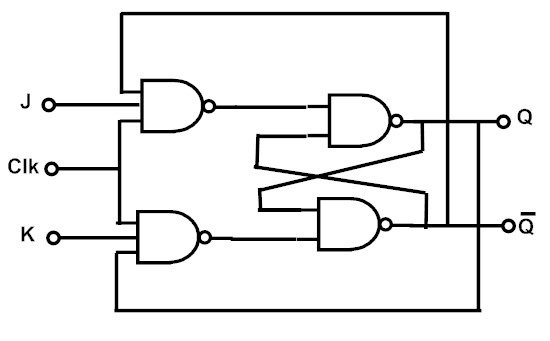

例子: j - k触发器。

请注意锁存器和触发器之间的唯一区别是锁存器对控制信号(时钟或使能)是电平敏感的,而触发器对控制信号(通常是时钟)是边缘敏感的。

触发

定义

触发器的输出变化可以通过输入信号的微小变化来实现。这种微小的变化可以通过时钟脉冲来实现。这个时钟脉冲被称为触发脉冲。

一个触发器被称为“触发”,当一个触发脉冲被应用到输入,使输出发生变化。人字拖就是基本组件在寄存器和计数器中,以多位数字的形式存储数据。连接多个触发器形成一个顺序电路,所有这些触发器都需要触发脉冲。应用于输入端的触发脉冲的数量决定了计数器的数量。

有两种类型的触发:水平触发和边缘触发

水平触发

输出状态的变化取决于输入的活跃程度的触发过程称为“电平触发”。

水平触发有两种类型,它们是

1.高级触发。

2.低电平触发。

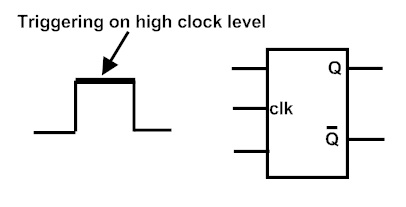

高水平触发

在高电平触发中,触发器的输出只有在其使能输入处于高状态时才会改变,即逻辑高或逻辑1。高电平触发的符号表示如下所示。

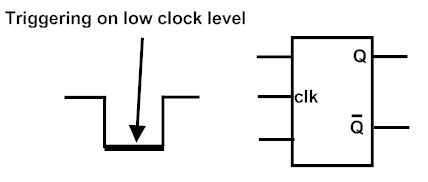

低电平触发

在低电平触发中,只有当其使能输入处于低状态时,即逻辑低或逻辑0,触发器的输出才会改变。低电平触发的符号表示如下所示。低电平触发通常由时钟输入上的气泡来识别。

边缘触发

在边缘触发中,只有当输入出现在时钟脉冲的任意一个转换时,即从低到高(0到1)或从高到低(1到0),输出才会改变。

边缘触发有两种类型,它们是

1.积极的边缘触发。

2.下降沿触发。

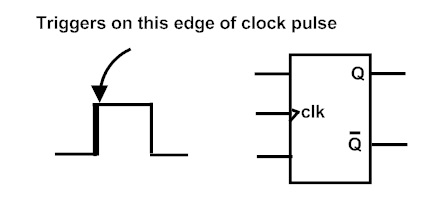

积极的边缘触发

在正边缘触发中,只有当输入在时钟脉冲输入的正边缘,即从低到高(0到1)的转换时,输出才会改变。

当要求触发器在低能级到高能级跃迁状态下响应时,采用正向边缘触发法。正边缘触发的符号表示如下所示。

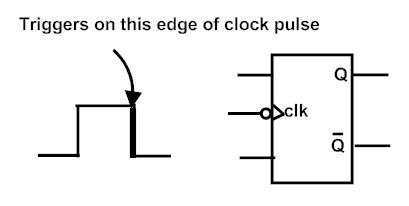

下降沿触发

在负边缘触发中,只有当输入在时钟脉冲输入的负边缘,即从高到低(1到0)的转换时,输出才会改变。

负边缘触发法用于要求触发器在高能级到低能级跃迁状态下响应的情况。负边触发的符号表示如下所示。

边缘触发器比关卡触发器好

最好使用边缘触发而不是水平触发。这是因为在电平触发触发器的特定情况下,当触发器的输出发生变化时,时钟脉冲同时给输入端,电平触发可能会导致电路不稳定。从输出到输入的反馈导致了这种不稳定。为了避免这种不稳定性,使用了边缘触发触发器。

3反应

我非常感谢你,这对我理解顺序电路的整个概念很有帮助。

Thankuw太多

感谢这是非常容易理解的顺序电路的整个路径简要。