介绍

JK Flip - Flop以发明IC的电气工程师Jack Kilby的名字命名。jk flip - flop被称为通用可编程翻转 - flop,因为使用其输入j,k预设和清晰,可以模仿任何其他flop的功能。

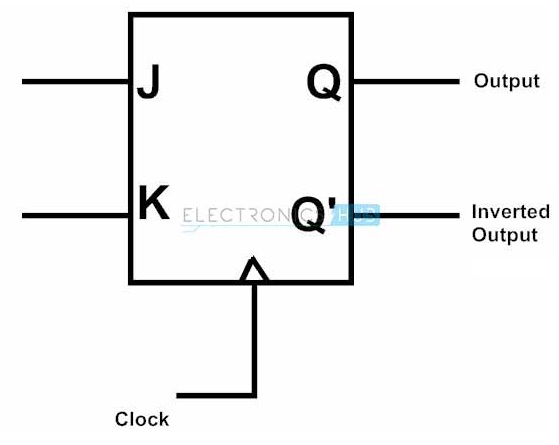

JK翻转 - 拖失板是Sr Flip的修改 - 没有非法状态的插槽。在此中,J输入类似于SR Flip - flop的集合输入,K输入类似于SR Flip - flop的重置输入。JK翻转的符号 - 拖鞋如下所示。

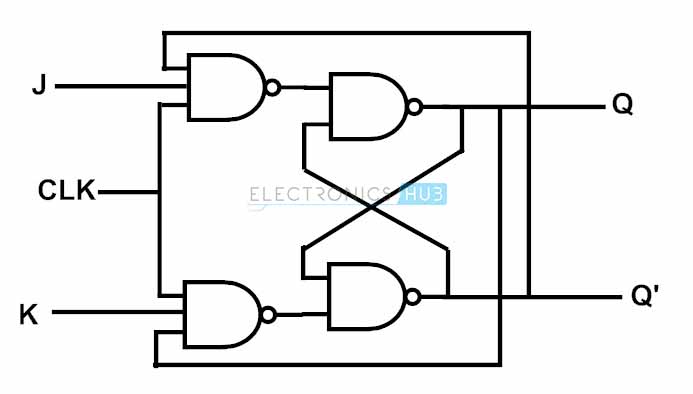

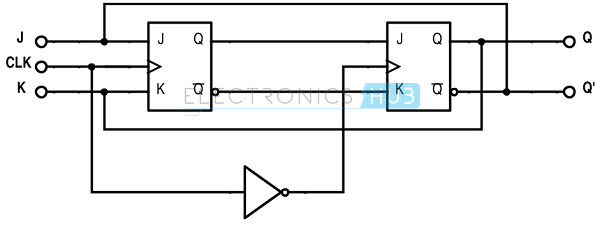

JK触发式逻辑图

JK翻转 - flop逻辑图如下图所示。如前所述,JK Flip - flop是SR Flip - flop的修改版本。逻辑图由三个输入NAND门组成,代替了SR Flip中的两个输入NAND门 - flop,输入被S和K的J替换为J和K。

The design of the JK flip – flop is such that the three inputs to one NAND gate are J, clock signal along with a feedback signal from Q’ and the three inputs to the other NAND are K, clock signal along with a feedback signal from Q. This arrangement eliminates the indeterminate state in SR flip – flop.

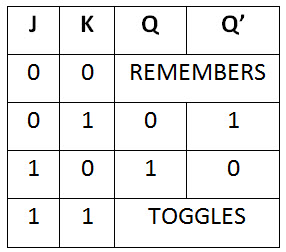

真相表

手术

情况1:当两个输入J和K都较低时,Q返回其先前的状态值,即它保存先前的数据。

当我们将时钟脉冲应用到J K触发器上并且J输入较低时,无论其他NAND门如何,NAND GATE-1输出都会变高。以相同的方式,如果k输入较低,则NAND GATE-2的输出也很高。因此,输出保持在相同的状态,即触发状态没有变化。

情况2:当j较低并且k较高时,触发器将处于重置状态,即q = 0,q’= 1。

当我们将时钟脉冲应用于j K触发器时,输入为j很低,k很高,k为高的输出,连接到j输入的NAND门的输出变为1。然后Q变为0状态。因此,触发器将处于重置状态。

案例3:当j高并且k较低时,翻转 - 翻牌将处于设定状态,即q = 1,q’= 0

When we apply a clock pulse to the J K flip flop and the inputs are J is high and K is low the output of the NAND gate connected to K input becomes 1. Then Q’ becomes 0. This will set the flip flop with the high clock input. So the Flip flop will be in SET state.

情况4:当两个输入j和k都高时,翻转 - 拖失位处于切换状态。这意味着输出将补充先前状态。

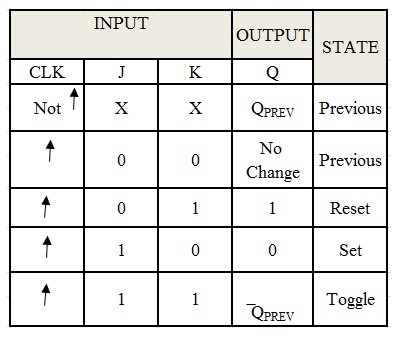

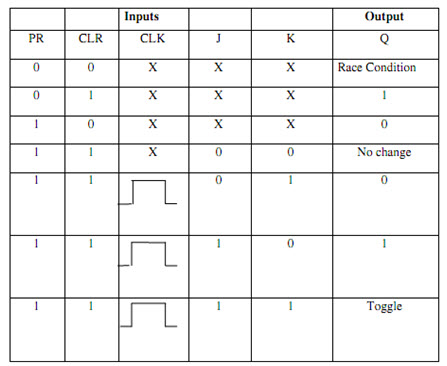

真相表

JK Flip的真实表 - 拖鞋如下所示。

围绕JK Flip flop的状况竞争

对于J K触发器的高输入,只有下部的大门是由相互补充的输出触发的,即Q和Q’。因此,尽管高输入连接到翻转 - 在任何瞬间启用一个门,但将禁用另一个门。如果上门处于残障状态,它将驱动触发器插槽到设置状态,稍后在启用下门时,它将驱动触发器以重置导致输出切换的状态。这将导致比赛围绕J K Flip - flop。

避免赛车状况的步骤

- 我们可以通过设置时钟时间小于触发器的传播延迟来避免围绕条件。可以通过边缘触发来实现。

- 通过使触发器在一个时钟周期内切换。这个概念是在主人奴隶触发器中引入的。

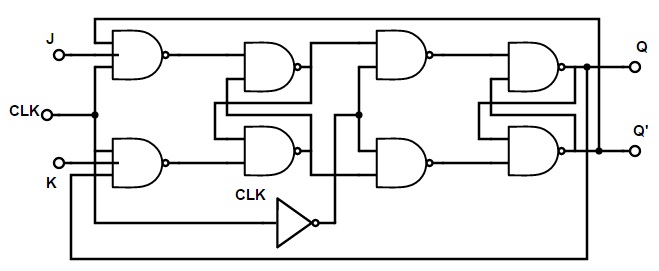

主奴隶JK拖利

主奴隶j k触发器是一种“同步”设备,允许数据通过时钟信号的时间传递。主 - 奴隶触发器由两个时钟的flip - 串联连接的触发器组成,它们将输入从输出中分离出来,因此术语“主 - 从属”。除了消除正常JK Flip中的问题 - 拖鞋,主人 - 奴隶JK Flip -flop还可以模仿SR Flip的功能 - 翻牌,时钟翻转 - 拖鞋,D Flip - Flop和Toggle Flip - Flop - flop。从属翻转的Q和Q’输出 - 拖失板被馈回主翻转 - 拖失板,而主翻转的输出 - 拖失板作为从属翻转的输入之一 - 拖失板。

当时钟输入较高时,主是活动的,并且从属不活动。根据输入,设置或重置主插脚的输出,并且从属触发器的输出不会更改,因此它保持在先前的状态。随着从属触发器在低时钟输入下变得活跃时,从flip的输出变化。当时钟较高时,主翻转的输出 - 拖放被搁置,因为在此期间从属不活动。当时钟较低时,主翻转的输出 - 触发器会被从flip看到 - flop并将其传递到输出。从属触发器的输出是主人的最终输出 - 从flip - flop。最终输出可在时钟脉冲的末端可用。

建造

主奴隶JK翻转 - 拖失式是两个SR flip - 拖鞋的级联组合,并具有从从输出到主人输入的反馈。大师的电路 - 奴隶翻转 - 拖失板如下所示

正时钟脉冲施加到主触发器上,并在应用于从属上,即主flop - flop在阳性转变期间是活跃的,而从属翻转 - flop在负转变期间是活跃的。在时钟的正边缘期间,输入J和K的数据传递给主翻转 - 失败,并将其固定在那里,直到时钟的负边缘过渡发生。然后,数据或信息传递给从属翻转 - 失败,此处收集了输出。

主人的符号表示 - 带有两个JK flip的奴隶jk翻转 - 拖鞋 - 拖鞋如下所示。

主人表的真实表 - 从奴隶JK翻转 - 与预设和清晰的输入一起翻牌。

当时钟输入较低时,并且主触发器的两个输入即J和K输入将不会影响主从属触发器的输出。

当时钟输入很高时

- 如果j很低,k很低:状态不变。

- 如果j很低,k很高:主奴板拖失板将处于重置状态。

- 如果j很高,k很低:主奴板拖失板将处于固定状态。

- 如果j很高,k很高:切换状态。

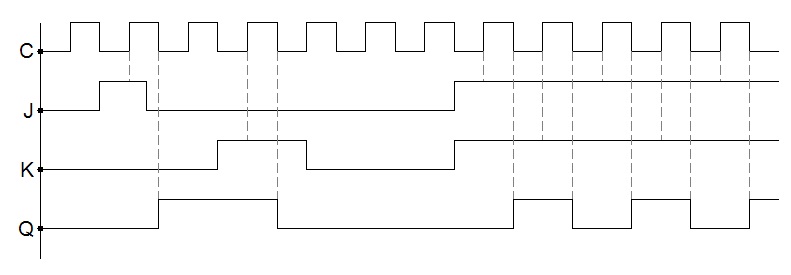

正时图

输入脉冲的宽度可能比触发器的传播延迟较小或多,它不会影响输出状态。但是,如果不违反设置和保留时间,则J和K输入在正时钟正边缘的值将影响主的输出状态 - 从属翻转 - 失败。

申请

JK Flip - 拖鞋是数字电子中使用最广泛的拖鞋之一。这是因为它们的通用可编程功能。

JK Flip的某些应用 - flop包括

•换档寄存器

•频率分隔线

•切换应用程序

•并行数据传输

•序列数据传输

•二进制计数器

•序列检测器

JK触发器的应用之一是切换。这在下面说明。

JK触发器开关

当我们将时钟信号应用于JK Flip - flop时,输入时钟信号的正转换可以实现当前的SATE输出的切换。这种启用条件不会继续贯穿时钟信号的正循环。翻转的J和K输入 - 触发器不能导致时钟脉冲的过渡。但是,在正转换时的输入值将根据其值确定输出。这是JK Flip - flop的应用之一。JK Flip的输出行为 - 借助波形的帮助,如下所示,flop的正向过渡的触发