定义:

锁存器是一种具有两种稳定状态的电子逻辑电路,即双稳态多谐振荡器。闩锁具有保留信息的反馈路径。因此,锁存器可以是存储器设备。只要设备通电,闩锁就可以存储一位信息。当enable被断言时,latch在输入改变时立即改变存储的信息,即它们是电平触发设备。当启用信号打开时,它连续对输入进行采样。

锁存电路可在两种状态下工作,具体取决于触发信号的高或低:激活–高或激活–低。

- 在有源-高锁存电路的情况下,通常两个输入都是低电平。该电路由任一输入上的瞬时高电位触发。

- 在有源-低锁存电路的情况下,通常两个输入都是高电平。该电路由任一输入上的瞬时低电压触发。

高级闩锁

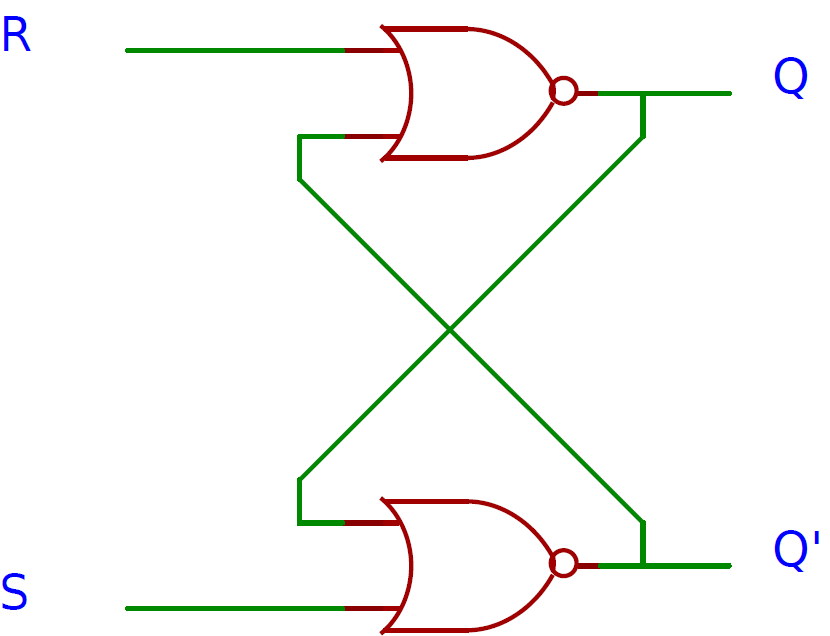

为了构造一个简单的锁存器,我们可以使用静态门作为基本构造块,并且可以通过向一个或非门电路引入反馈来构造两个或非门。

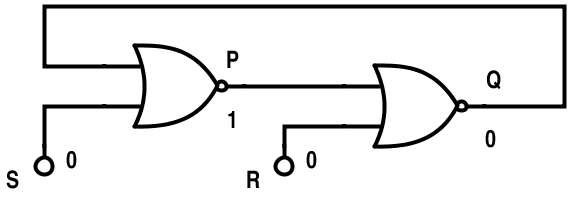

下面显示了一个带有反馈的简单或非门逻辑。

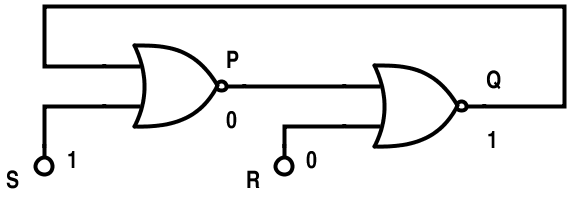

这里,输入S和R都是0(S=R=0)。第一个或非门的输出为P=1。这与R=0一起馈送至第二个或非门。因此,第二栅极的输出为Q=0。电路处于稳定状态,P=1,Q=0。如果我们设S=1,那么P=0。这将使Q=1,如下所示。

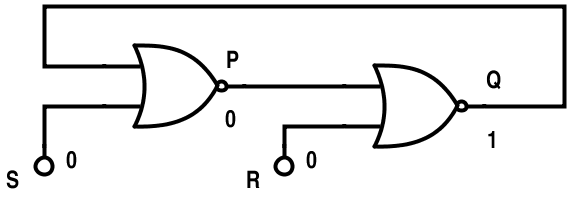

这也是一种稳定状态。如果S为0,则没有变化,因为Q=1反馈给第一个NOR,P仍然为0。如下图所示。

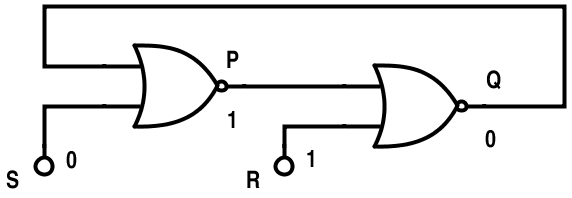

如果R为1,那么Q变为0,这将把P变回1。

如果R为0,则没有变化,我们到达了开始的位置。

由于输出不仅取决于当前输入,而且还取决于过去的输入序列,因此该电路被称为具有存储器。如果不允许输入条件S=R=1,则稳态输出总是互补的。当S和R都等于1时,P=0和Q=0,这与互补条件相矛盾。因此,输入条件S=R=1被认为是不允许的。锁存电路始终绘制为交叉耦合形式,以强调门之间的对称性。

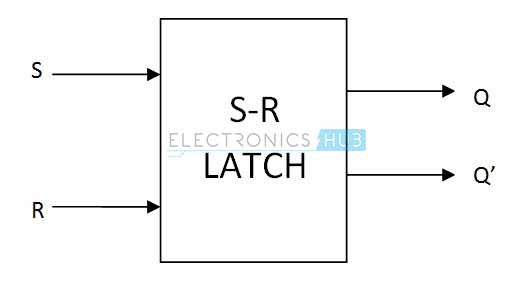

在该电路中,当S=1时,将输出Q“设置”为1,当输入R=1时,将输出Q“重置”为0。在S=R=1的限制下,该电路称为设置复位锁存器(SR锁存器)。

绕场条件

在逻辑电路中,竞态条件是指“一个逻辑电路的两个输入同时发生变化,从而使输出处于暂时状态的情况”。为了改变产出,投入在竞争中。它通常发生在以输出作为电路反馈输入的设备中。当设备试图同时执行两个操作(即同时改变两个输入的状态)时,会出现不必要的情况。我们很少有办法避免这种情况,比如使用边缘触发或使用主从触发器。

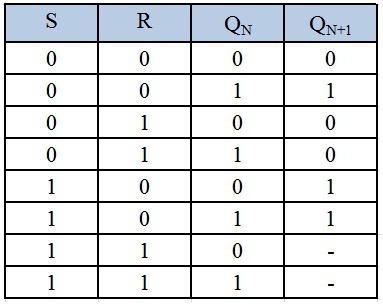

SR锁存器的状态转换表或真值表

状态表类似于组合电路中的真值表,它提供了有关电路状态的信息。由于时序电路的输出取决于当前和以前的状态,因此它们以称为状态表的表格的形式表示,并根据当前状态和其他输入显示下一个状态。

SR闩锁的状态表如下所示。

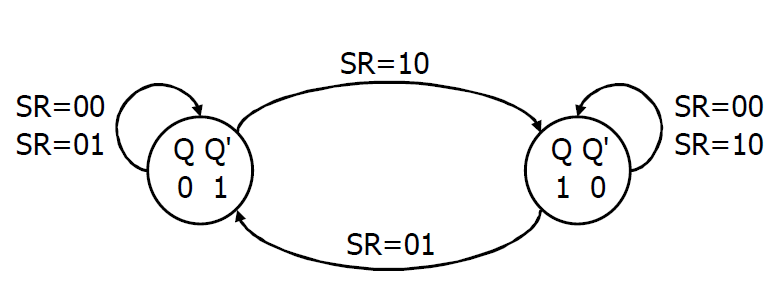

状态图

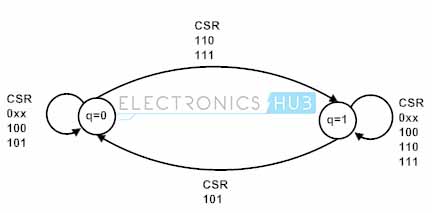

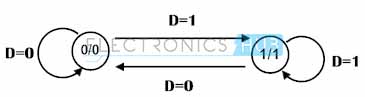

除了表格和方程外,状态机(或系统)还可以用状态图表示。在此状态图中,状态由圆表示,状态之间的转换由连接圆的直线或圆弧表示。简单SR锁存器的状态图如下所示。

状态图提供状态表可以拥有的所有信息。这是直接从状态表中获得的。

选通S-R锁存器

通常,锁存是透明的,即当输入发生变化时,输出立即发生变化。但对于许多应用程序,最好有一个独立的周期,即使输入发生变化,输出也不会发生变化。在此期间,输出被称为真正的“锁定”。这可以通过使用额外的输入(启用或时钟或门)来实现。如果未断言启用(或时钟或门)信号,则忽略输入,并将输出锁定到先前的值。为了使用这个额外的信号,应该添加额外的逻辑。这些电路称为门控或时钟锁存器。

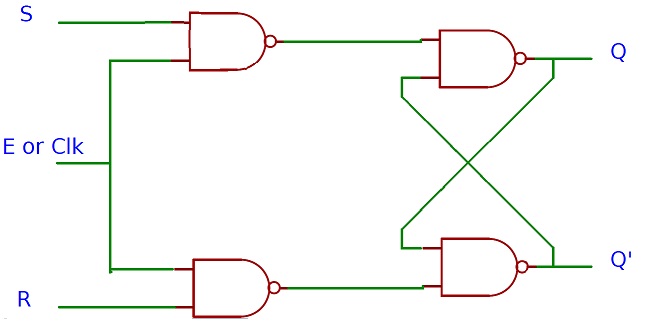

选通SR锁存器可以通过两种方式实现:向SR锁存器添加第二级与门,或向̅S̅R锁存器添加第二级与非门(反向SR锁存器)。

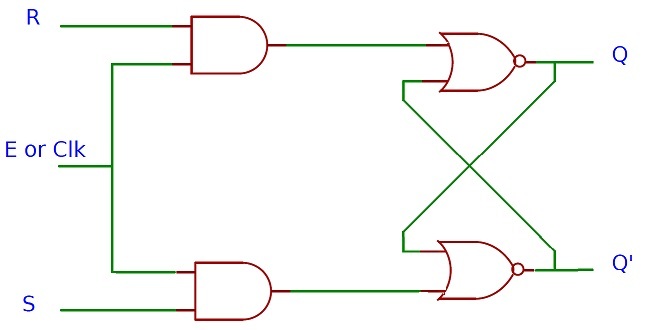

由NOR门构成的选通SR锁存器电路图如下所示。

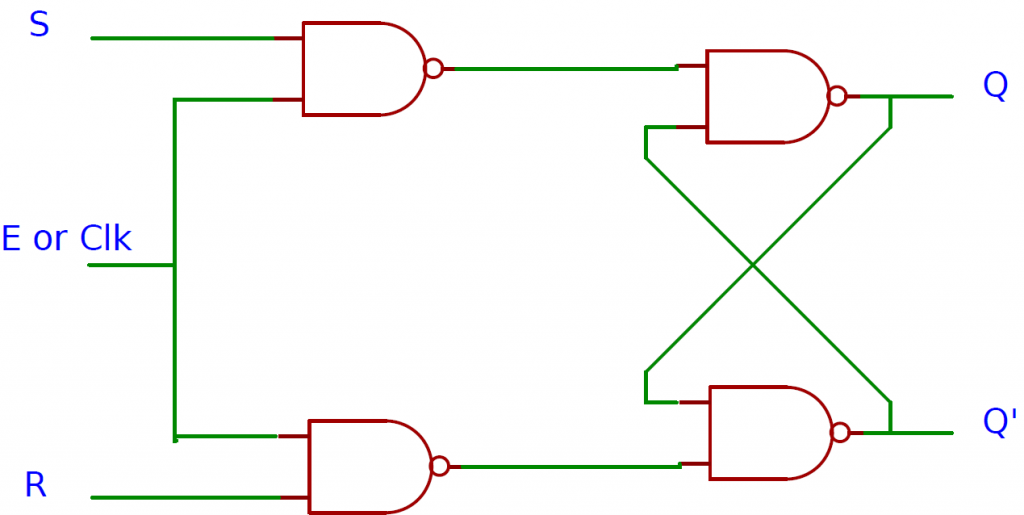

由与非门构成的选通SR锁存器电路图如下所示。

当与非门反转输入时,̅S̅R锁存器变为选通SR锁存器。

当enable(或clock)为high(高)时,表示锁存器已启用,即输出响应输入。

当enable(或clock)为low(低)时,闩锁被禁用并保持在该状态,直到enable被断言。

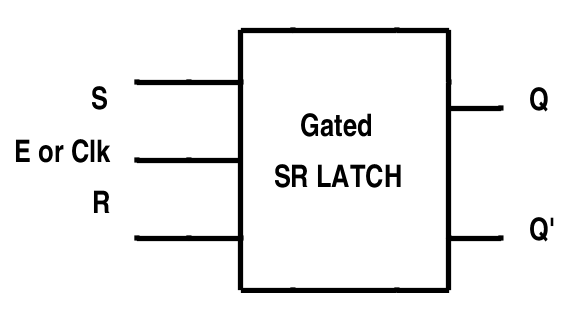

门控SR闩锁的符号如下所示

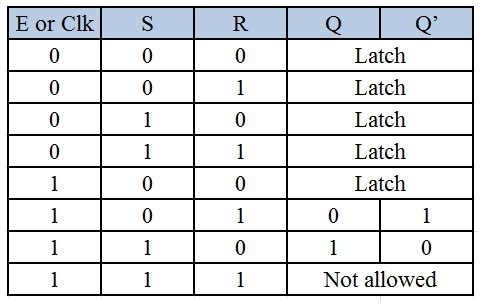

门控SR闩锁的真值表如下表所示。

门控SR锁存器的状态图如下所示。

D闩锁

数据锁存器或延迟锁存器(D锁存器)是存储数据的简单锁存器之一。它也被称为透明闩锁。一个简单的D锁存器可以由两个与非门构成。

当S=R=1时,SR锁存器中出现的绕场情况可以在D锁存器中避免,因为R输入被替换为倒S(重命名为D)。因此,不存在非法或禁止输入。在D锁存器中,Q始终是D。

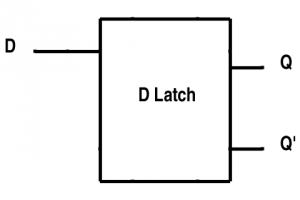

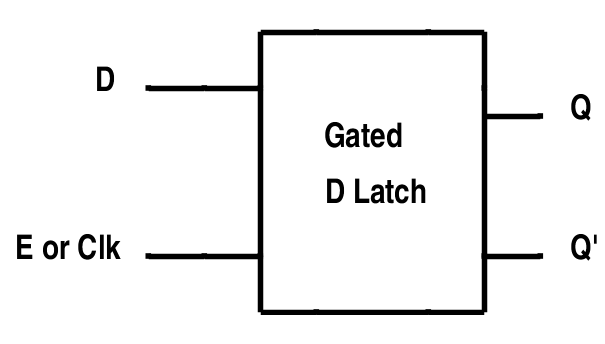

D闩锁的符号如下所示。

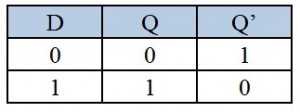

这些简单的D锁存器不经常使用,但选通D锁存器非常常见。简单D锁存器的真值表如下所示。

门控D锁存器

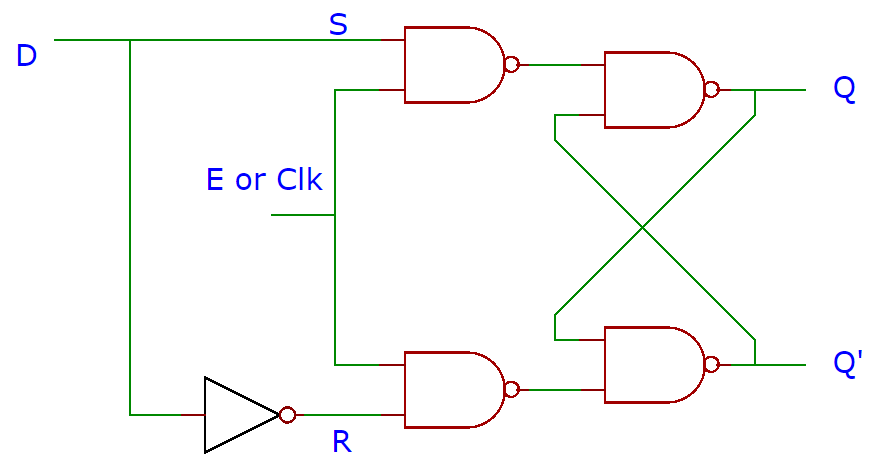

通过修改选通SR锁存器,可以轻松构造选通D锁存器。对选通SR锁存器的唯一修改是R输入必须更改为反向S。由NOR SR锁存器形成的选通锁存器如下所示。

当时钟或启用为高电平(逻辑1)时,输出锁存D输入上的任何内容。当启用或时钟低(逻辑0)时,最后一次启用高的D输入将作为输出。

该锁存电路将永远不会经历“竞争”状态,因为单D输入被反转以提供给两个输入。因此,不可能有相同的输入条件。因此,D锁存电路可以安全地用于任何电路中。

门控D闩锁的符号如下所示。

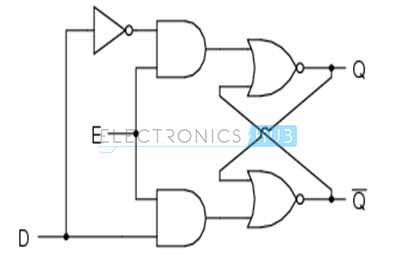

与选通NOR SR闩锁类似,也可以从选通NAND SR闩锁构造选通D闩锁。门控NAND SR larch的门控D锁存器电路如下所示。

可以避免使用反相器,因为可以使用与非门来获得反转值。需要对上述电路进行一些修改,结果电路如下所示。

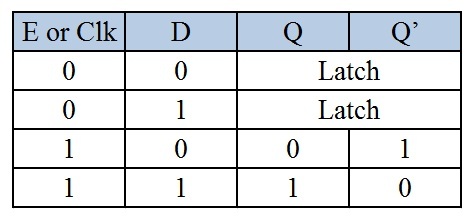

选通D锁存器的真值表(或状态表)如下所示。

s选通D锁存器的状态图如下所示。

应用

- 它们是基本的1位内存设备。

- D锁存器通常用作异步系统中的I/O端口。

- 数据锁存器有时用于同步两相系统,以减少晶体管计数。

插销的优点

- 锁存器速度更快,因为它不需要等待时钟信号,所以它们在高速设计中最常用。

- 它们需要更少的动力。

- 基于闩锁的设计具有较小的模具尺寸。

- 闩锁的主要优点是“借用时间”。其中,如果一个操作未在规定时间内完成,则执行该操作所需的时间将从另一个操作时间借用。

闩锁的缺点

- 闩锁不太可预测,因为有更多的机会影响比赛条件。

- 电平敏感器件,因此亚稳态的可能性更大。

- 由于锁存电路具有电平敏感特性,因此很难对其进行分析。

一个回答

这是一部了不起的作品。我非常感激。