在本教程中,我们将了解一个名为Demultipleer的有趣的数字逻辑电路,也称为Demux。学习什么是多路分解器,常用的解码器配置是什么,如1-2,1至4,1对8,也是多路分解器的一些应用。

介绍

在之前的教程中,我们学习了多路复用器或者只是MUX。多路复用器是一种简单的组合逻辑电路,它从多个输入端中选择一个并将其通过单个输出端。MUX是负责多路复用的设备。

解复用器的动作或操作与多路复用器的动作或操作完全相反。与MUX相反,Demux是一对多的电路。通过使用解复用器,来自一个输入的数据可以传递到多个输出数据线中的一个。

多路分解器主要用于布尔函数发生器和解码器电路。不同的输入/输出配置多路分解器以单个集成电路(ICS)的形式提供。

此外,还有一个将两个或多个DEMUX电路级联的设施,以产生多个输出解复用器。让我们在本教程中简要了解解复用器及其类型。

什么是解复用器?

从一个输入中获取信息,并在多个输出中的一个上传输该信息的过程称为解复用。如果您还记得多路复用器教程,我们在那里讨论了多路复用的概念。而解多路复用恰恰相反。

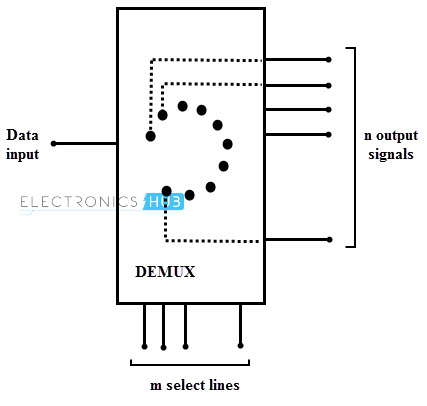

多路分解器是组合逻辑电路,其接收关于单个输入线的信息,并通过'n'可能的输出线中的一个发送相同的信息。

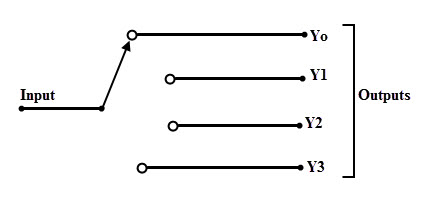

为了选择特定的输出,我们必须使用一组选择线,并且这些选择线的比特组合控制特定输出线的选择以连接到给定的即时的输入。下图说明了解复用器的基本思想,其中在给定的瞬间可以将输入切换到四个输出中的任何一个。

如果多路复用器被称为数据选择器,那么解复用器被称为数据分发器,因为它们将输入端接收到的相同数据传输到不同的目的地。

因此,一个解复用器是一个1-to-N设备,而作为多路复用器是一个N-to-1设备。下图显示了解复用器或简单的DEMUX的框图。

它由1个输入行,' n '输出行和' m '选择行组成。在这种情况下,需要m条选择线来产生2米可能的输出行(考虑2米= n)。例如,1到4的解复用器需要2 (22= 4)选择行以控制4个输出线。

基于输出配置,诸如1:2,1:4,1:8和1:16的输出配置有几种类型的多路分解器。

这些可在不同的IC封装和一些最常用的解复用IC包括74139(双1:4 DEMUX), 74138 (1:8 DEMUX), 74237 (1:8 DEMUX与地址锁存),74154 (1:16 DEMUX), 74159 (1:16 DEMUX开路集电极类型)等。

注意:多路分解器IC也称为解码器IC。例如,74159是4行到16行解码器IC。

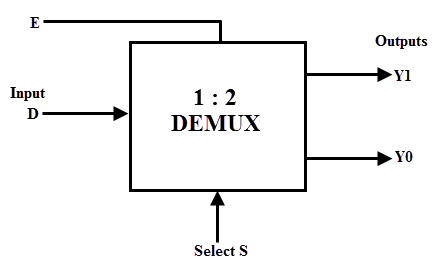

1 - 2信号分离器

一种1- 2解复用器由一条输入线、两条输出线和一条选择线组成。选择行上的信号有助于将输入切换到两个输出之一。下图显示了带有附加输入的1- 2解复用器的框图。

在图中,只有两种可能的方式连接输入到输出线,因此只有一个选择信号就足够做解复用操作。当选择输入为LOW时,输入将被传递给Y0,如果选择输入为HIGH,则输入将被传递给Y1。

1- 2解复用器的真值表如下所示,其中根据选择输入S的值,输入被路由到Y0和Y1。

| 年代 | D | Y1. | y0. |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 |

我们可以为输出导出的布尔表达式如下:

假设S为Select Input, D为Data Input, Y0和Y1为1- 2解复用器的输出。由上表可知,当选择线和输入线的组合分别为低活跃和高活跃时,输出Y0是活跃的,即:S d = 0 1.

因此输出Y0的表达式为

Y0 =年代D

Similarly, the output Y1 is active when the combination of select line and input line are active high, i.e.,S d = 11.

因此输出Y0的表达式为

y = s d

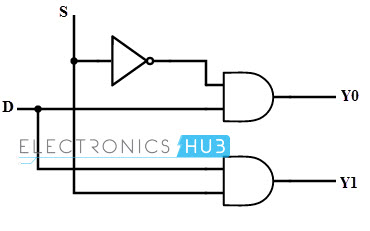

根据上面的真值表和推导出的布尔表达式,可以用如下图所示的两个和门和一个非门设计出1到2解复用器的逻辑图。当选择行S = 0时,第一个和门(A1)被启用,而第二个和门(A2)被禁用。

然后,输入的数据流到输出行Y0。类似地,当S = 1时,第二个和门(A2)被启用,而第一个和门(A1)被禁用,因此数据被传递到Y1输出。

1到4信号分离器

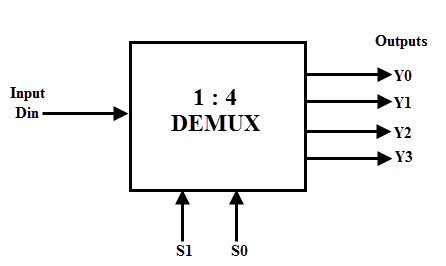

1至4个多路分解器具有单个输入(d),两个选择线(S1和S0)和四个输出(Y0至Y3)。对于特定时间的选择线组合,输入数据将在给定时间转到四个输出中的任何一个。

这个解复用器也被称为2- 4解复用器,这意味着它有两条选择线和四条输出线。一个1:4 DEMUX的框图如下所示。

这类解复用器的真值表如下所示。由真值表可知,当S0 = 0, S1 = 0时,数据输入连接输出Y0;当S0 = 0, S1 =1时,数据输入连接输出Y1。

类似地,其他输出连接到其他两个选择行组合的输入。

| S1 | S0 | D | Y3. | Y2. | Y1. | y0. |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 0 | 0 | 0 |

从上面的真值表中,我们可以推导出输出的布尔表达式如下:

Y0 =S1S0D

日元=S1S0 D.

Y2 = S1S0D

Y3 = S1 S0 D.

其中D为输入数据,Y0 ~ Y3为输出线,S0和S1为选择线。

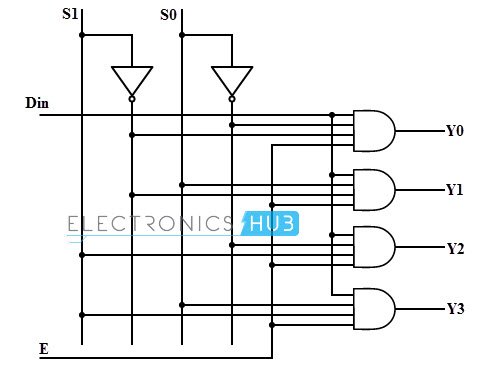

从上面的布尔表达式,可以通过使用四个3输入和栅极和两个不栅极来实现1到4个多路分解器,如下图所示。两个选择线一次启用特定和门。另外,存在启用/选通输入,其充当全局使能输入I.E.,仅当'E'位高时,输出仅处于活动状态。

因此,根据选择输入的组合,输入数据通过所选门来传递给关联的输出。

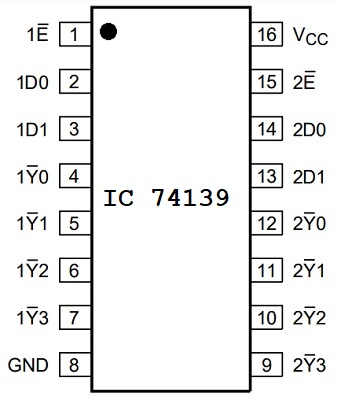

This type of demultiplexer is available in integrated circuit form as IC 74139. It one of the most commonly used demultiplexer ICs and it is a dual 1-to-4 demultiplexer IC i.e., it contains two independent 1-to-4 demultiplexer blocks in one IC. Each DEMUX accepts two binary inputs as select lines and four mutually exclusive active-low outputs.

两种多路分解器都有单独的选择线条,因此它们可以充当真正独立的解码。此外,每个多路分解器包括专用使能引脚,它可以充当解复用器操作的数据输入。使能引脚很低。

输出是激活的LOW,即默认为HIGH。因此,如果使能引脚是HIGH,所有的输出都是HIGH,如果使能是LOW,那么基于选择引脚,只有相应的输出引脚是LOW。

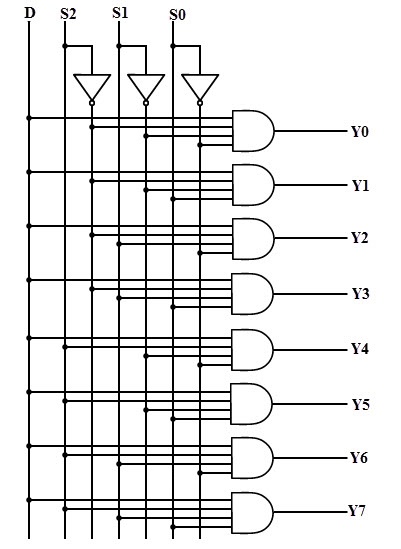

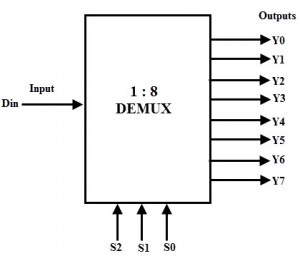

1至8信号分离器

下图显示了由单个输入D组成的1对8个多路分解器的框图,三个选择输入S2,S1和S0以及来自Y0至Y7的八个输出。

由于其三个选择输入线和8个输出线,它也被称为3至8分切换器。根据选择输入的组合,它将一个输入线分配到8个输出线中的一个。

1到8解复用器的真值表如下所示。输入' D '与从Y0到Y7的8个输出中的一个连接,这是基于所选择的行S2, S1和S0。

例如,如果S2 S1 S0 = 0 0 0,则输入D连接输出Y0,以此类推。

| S2 | S1 | S0 | Y7. | y6. | y5. | Y4. | Y3. | Y2. | Y1. | y0. |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | D |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | D | 0 |

| 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | D | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 0 | 0 | D | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 0 | 0 | D | 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 0 | D | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | D | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | D | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

从这个真值表中,所有输出的布尔表达式可以写成如下所示。

Y0 =S2S1S0D

日元=S2S1S0 D.

Y2 =S2S1S0D

Y3 =S2S1 S0 D.

Y4 = S2S1S0D

Y5 = S2S1S0 D.

Y6 = s2S0D

Y7 = s1s0d

由这些得到的方程,该解复用器的逻辑图可以用8个4输入和门和3个NOT门来实现,如下图所示。选择线的不同组合在给定时间激活一个和门,这样数据输入就会出现在相应的输出上。

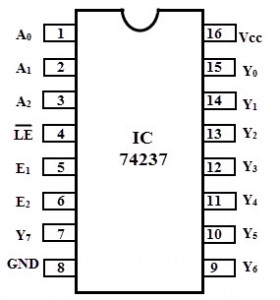

目前有两种流行的1到8解复用集成电路。一个是IC 74237,它由三个选择输入的锁存器组成。这个IC的引脚如下所示。

引脚A0到A2为数据输入,Y0到Y7为解复用器输出,e1和e2分别为有源-低数据使能引脚和有源-高数据使能引脚,LE为锁存使能输入,Vcc和GND端子为正电源电压和接地端子。

该集成电路结合了3位存储锁存器和3- 8解码器功能。

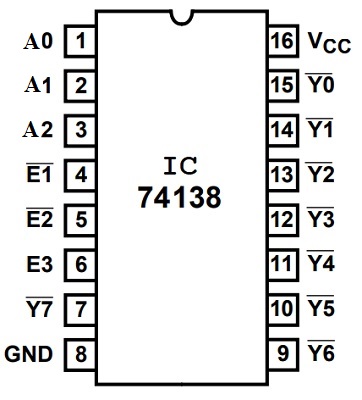

另一个常用的1-o至8分解器集成电路是IC 74138。除了没有锁存器启用输入之外,引脚放电非常相似(因为所有使能引脚是正常的使能引脚 - 两个是高电平的,一个是高电平的,并且一个是有效的。并且输出处于高电平。以下图像显示了74138 IC的引脚。

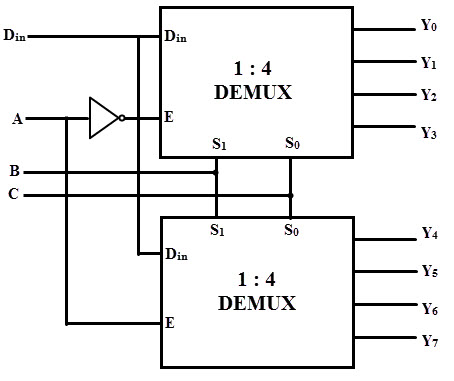

1- 8 DEMUX使用两个1- 4解复用器

当应用需要更高阶的输出引脚数的解复用器时,单个集成电路是无法实现的。如果需要超过16个输出引脚,则级联两个或更多的解复用ic来满足要求。

例如,如果应用程序需要来自deux的32条输出线,那么我们级联两个1:16解复用器或三个1:8解复用器。因此,通过级联两个或多个解复用器,可以实现一个大型解复用器。

考虑通过使用具有适当级联的两个1到4个多路分解器来实现1到8个多路分解器的情况。

在上图中,选择输入的最高有效位A连接到使能输入,这样它在连接到一个DEMUX之前是互补的,并直接连接到另一个。

这个配置,当一个被设置为零,其中一个输出线Y0 Y3选择组合的基础上选择线B和c,同样的,当一个被设置为1,根据选择线的一个输出行Y4日元将被选中。

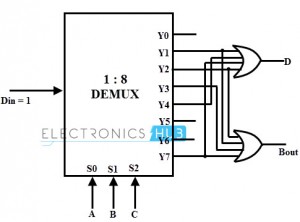

使用1- 8 DEMUX实现全减法器

类似于多路复用器,多路分解器也用于布尔功能实现以及组合电路设计。我们可以通过正确控制选择线来设计多路分解器来生产任何真理表输出。

考虑实现解复用电路以产生全减法器输出的情况。真值表显示了一个完整减法器的输出。

| 一个 | B | B在 | D | B出去 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

从上表中,完整的减法器输出D可以写成

D = f (A, B, B在)

D =∑m (1,2,4,7)

D =一个BB在+一个BB在+一个BB在+ a b b在

借款输出可以表示为

B出去= f (A, B, B在)=Σm(1,2,3,7)

B出去=一个BB在+一个BB在+一个B B.在+ a b b在

从这些布尔表达式中,可以通过正确配置1到8的DEMUX来构建产生完整减法器输出的解复用器,例如当输入D = 1时,它在输出处给出minterms。

通过对这些minterms进行逻辑ORing,可以得到差值和借值的输出,如图所示。

多路分解器的应用

由于多路分解器用于选择或启用许多信号,因此这些信号广泛地用于微处理器或计算机控制系统,例如:

- 选择用于数据传输的不同IO设备(数据路由)

- 选择不同的存储库(存储解码)

- 根据地址,启用不同的存储芯片行

- 启用不同功能单元。

除此之外,多路分解器可以在各种应用中找到:

- 同步数据传输系统

- 布尔函数的实现(正如我们在上面讨论的完整的减法函数)

- 数据采集系统

- 组合电路的设计

- 自动测试设备系统

- 安全监控系统(一次选择特定监控摄像机)等。

结论

一个完整的初学者或解码器的指南。您学习了多路分解器,不同类型的解码器,如1到2,1至4,1至8,1至16,其逻辑电路以及多路分解器的一些重要应用。

12的反应

很好,很容易理解

可怕的信息。帮了我大忙谢谢你告诉我这么棒的信息

太感谢了

谢谢你提供的非常明确的信息

你在和图上有一个错误

Y6没有正确连接到“S0”,但没有连接到“not S0”

如果D的值是给定的,如00101011。然后我们如何使用3到8个解复用器得到输出。请尽快回复我,先生

太感谢了

不能比这更好到工程学生!!!谢谢你的惊人SM !!!

白痴,在deux Y6=Y7修复一个bug

用“谢谢”传递评论,但是错误提交没有通过。你疯了?

固定的。

Thanx非常高兴我很困惑我是课堂。我一直在做

在“1- 8 DEMUX使用两个1- 4解复用器”部分,我们如何完全禁用级联系统?