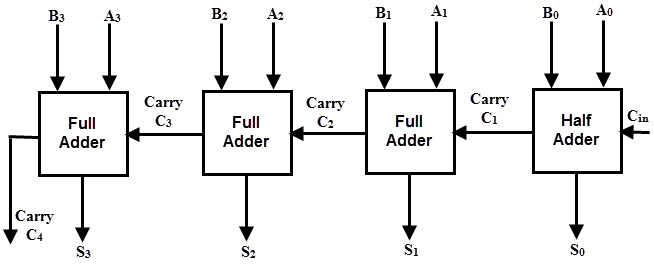

在并行加法器的情况下,当Eutend的所有位和加法器必须同时可用以执行计算时,启动两个数字的二进制添加。在并行加法器电路中,每个完整加法器级的携带输出连接到下一个高阶级的携带输入,因此它也称为纹波载型加法器。

在这样的加法电路中,在发生输入携带之前,不可能产生任何级的总和和输出。因此,在附加过程中将存在相当大的时间延迟,这被称为传播延迟。在任何组合电路中,信号必须在输出端子中可用之前通过栅极传播。

考虑上述图,其中,一旦将输入信号施加到它,就通过相应的完整加法器产生总和S4。但是随身稳态值的携带输入C4不能在其稳态值下提供C3。类似地,C3取决于C1上的C2和C2。因此,携带必须传播到所有阶段,以便输出S4并携带C5稳定其最终稳态值。

传播时间等于典型的栅极乘以电路中的栅极电平的数量的传播延迟。例如,如果每个完整的加法器阶段具有20n秒的传播延迟,则S4将在80N(20×4)秒后达到其最终正确值。如果我们延长添加更多位数的阶段数,那么这种情况变得更糟。

因此,并行加法器中添加的位数的速度取决于携带传播时间。但是,信号必须通过栅极传播给定足够的时间以产生正确或所需的输出。

以下是在并行加法器中获得高速的方法以产生二进制添加。

- 通过采用更快的延迟延迟,我们可以降低传播延迟。但每个物理逻辑门都会有一个能力限制。

- 另一种方法是增加电路复杂度以减少携带延迟时间。有几种方法可用于加速并行加法器,一种常用的方法采用通过消除阶段携带逻辑来进行外观的原理。

携带看法加法器

随身携带看法加法器是一个快速并行加法器,因为它通过更复杂的硬件降低了传播延迟,因此它是昂贵的。在这种设计中,对加法器的固定组的携带逻辑减少到两个级别的逻辑,除了纹波携带设计的转换。

该方法利用逻辑门,以查看增强和附加的较低订单位,以查看是否要生成更高阶携带。让我们详细讨论。

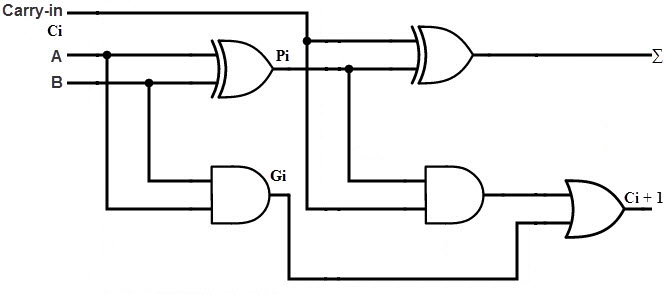

考虑上面显示的完整加法器电路与相应的真相表。如果我们将两个变量定义为携带生成GI并随身携带传播PI,那么

P.一世= A.一世⊕B一世

gi = ai bi

总和输出和携带输出可以表示为

si = pi⊕ci

C i +1 = gi + pi ci

如果GI是携带产生的携带,则无论输入携带如何,都是AI,BI的携带。PI是携带传播,并且它与来自CI的携带的传播相关联。

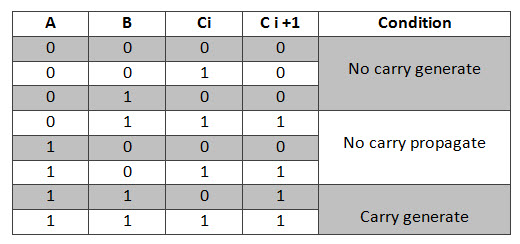

4阶段携带保护加法器中的每个阶段的携带输出布尔函数可以表示为

C1 = G0 + P0 CIN

C2 = G1 + P1 C1

= G1 + P1 G0 + P1 P0 CIN

C3 = G2 + P2 C2

= G2 + P2 G1 + P2 P1 G0 + P2 P1 P0 CIN

C4 = G3 + P3 C3

= G3 + P3 G2 + P3 P2 G1 + P3 P2 P1 G0 + P3 P2 P1 P0 CIN

从上面的布尔方程,我们可以观察到C4不必等待C3和C2传播,但实际上C4在C3和C2的同时传播。由于每个携带输出的布尔表达式是产品的总和,因此可以用一个级别的和门来实现,然后是一个或门。

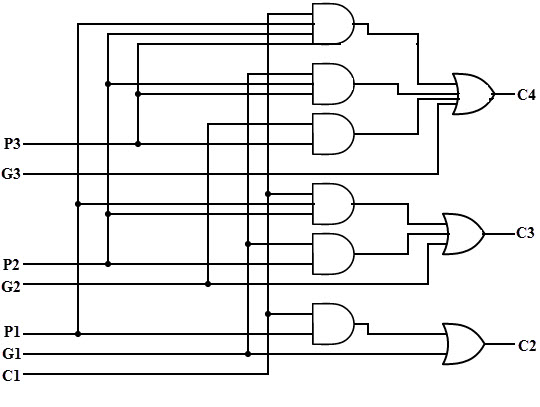

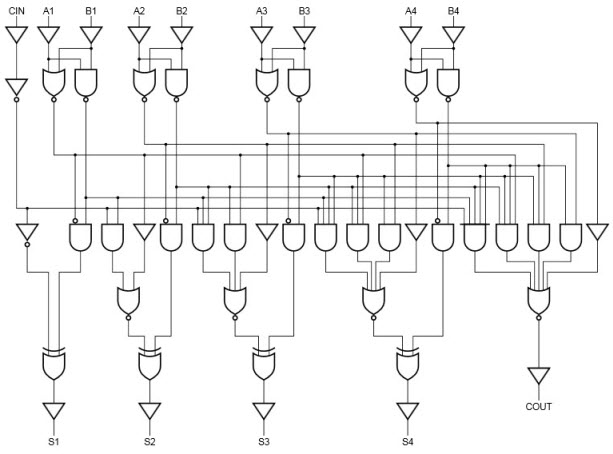

为下面的图中所示的携带超导携带发生器的每个携带输出(C2,C3和C4)的三种布尔函数的实现。

因此,可以利用带孔保护方案来实现4位并联加法器以增加二进制添加的速度,如下面的图所示。在此,每个总和输出需要两个前或门。第一ex-or门生成PI变量输出,并且AND门会生成GI变量。

因此,在两个门级别中,产生所有这些p和g。随身携带保护发生器允许所有这些P和G信号在它们稳定到其稳态值之后传播,并在两个级别的延迟时产生输出载波。因此,总和输出S2至S4具有相同的传播延迟时间。

还可以通过级联带有携带逻辑的4位加法器的数量来构建16位和32位并行加法器。通过级联具有两个更长的闸门延迟的四个4位加法器来构造16位携带保护加法器,而通过两个16位加法器的级联形成32位携带保护加法器。

在16位携带保护加法器中,需要5和8个栅极延迟,以分别获得C16和S15,其与C16和10级级级别的级联四位携带保护块中的C16和S15相比较少。类似地,如果32位加法器由八个4位加法器实现,则C32和S31,C32和S31需要在32位加法器,7和10栅极延迟,其少于相同输出的18和17栅极延迟。

携带看法加法器IC

高速携带保护剂加载剂在多个制造商中集成在不同位配置的集成电路上。有几个单独的携带发电机IC可用,以便我们必须与逻辑门进行连接以执行添加操作。

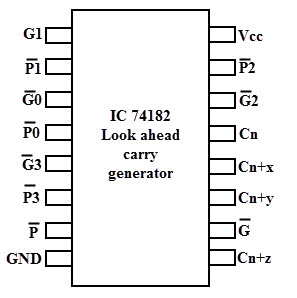

典型的携带 - 超强发电机IC是74182,其接受四对有效低携带传播(作为P0,P1,P2和P3),并且携带产生(GO,G1,G2和G3)信号和有源高输入(CN)。

它在四组二进制加法器中提供有效的高载波(CN + X,CN + Y,CN + Z)。该IC还促进了通过主动低传播并携带产生输出的其他级别。

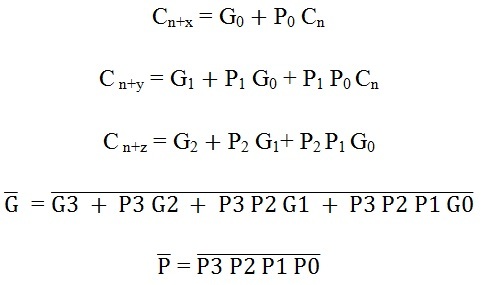

IC 74182提供的逻辑表达式是

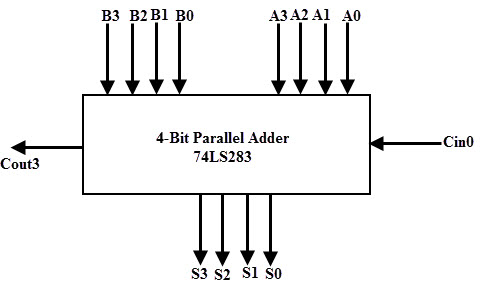

另一方面,存在许多高速加法器IC,其结合了一组具有随身携带保护电路的完整加法器。最流行的这种IC形式为74LS83 / 74S283,它是4位并联加法器高速IC,其包含四个具有带有携带主张电路的互连的全加入器。

此类IC的功能符号如下图所示。它接受两个4位数作为A3A2A1A0和B3B2B1B0,并将CIN0输入到LSB位置。该IC将输出总和位产生为S3S2S1S0,并将输出输出COUT3进入MSB位置。

通过级联两个或多个并行加法器IC,我们可以执行较大的二进制数,例如8位,24位和32位添加。