在本教程中,我们将学习二进制加和减电路。我们将学习半加法器、全加法器、并行加法器(使用多个全加法器)、半减法器、全减法器和并行加/减法器组合电路。

二进制加法电路

加法和减法是任何数字计算机都必须进行的两种基本算术运算。如果这两种操作都能正确实现,那么乘法和除法任务就会变得很简单(因为乘法是重复的加法,除法是重复的减法)。

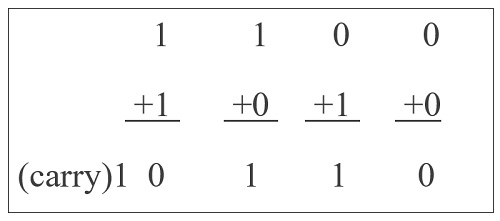

考虑两个二进制数相加的运算,这是数字计算机执行的基本任务之一。四种基本的加法运算两位二进制数分别是:

- 0 + 0 = 0

- 1 + 0 = 1

- 0 + 1 = 1

- 1 + 1 =(进位)10

在前三个操作中,每个二进制加法给出一个位的和,即0或1。但是对于第四个加法操作(输入为1和1),结果由两个二进制数字组成。这里,较低的有效位称为“和位”,较高的有效位称为“进位”。

对于单个位的添加,可能没有问题。当我们试图将二进制数加1位以上时,可能会出现这个问题。

用于实现两个二进制数相加的逻辑电路称为二进制加法器电路。根据它们处理“1+1”加法输出的方式,它们被分为:

- 一半加法器

- 完整的加法器

让我们看一看由各种加法器电路实现的二进制加法。

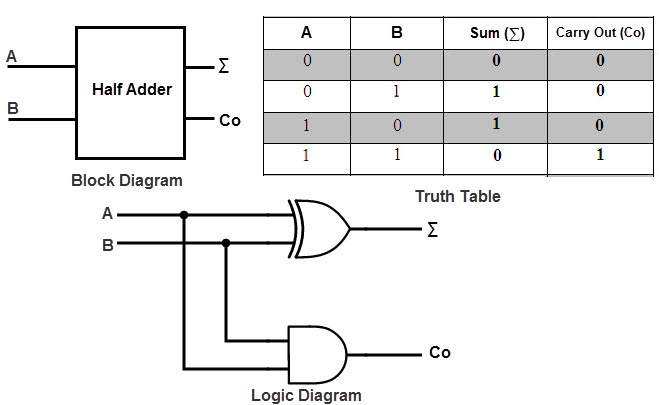

一半加法器

用于将两个1位或两个比特相加的逻辑电路称为半加法器电路。这个电路有两个输入和两个输出。输入是两个1位的二进制数(称为Augend和Addend),输出是Sum和进位。

下图显示了半加法器的框图。

半加法器的真值表如下表所示。

| 输入 | 输出 | ||

| 一个 | B | 总和 | 携带 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

如果我们观察上面真值表中的“和”值,它类似于一个Ex-OR门。类似地,上面真值表中“Carry”的值类似于“与门”。

所以,为了正确地实现半加法器,你需要两个逻辑门:一个用于“和”输出的异或门和一个用于“进位”输出的与门。下图显示了半加法器的逻辑图。

在以上的半加法器电路中,输入被标记为A和b,“和”输出被标记为求和符号(∑),进位输出被标记为CO.

半加法器主要用于一阶二进制数即1位二进制数的加数和加数的加法。我们不能对超过一位的二进制数进行加法,因为半加法器不能包含前一个和的进位信息。

由于这一限制,半加法器在许多应用中,特别是在多位数加法中,实际上是不被使用的。在这种应用中,前一位的进位加法必须加上两位;因此,这是一个三位数的加法。

完整的加法器

全加法器是一种组合逻辑电路,它对三个比特进行加法运算,产生两个输出:和和进位。如我们所见,半加法器不能对三个输入作出响应,因此用全加法器一次加三个数字。

它由三个输入组成,其中两个是输入变量,表示要加的两个有效位,而第三个输入终端是前一个加法的进位。这两个输出是Sum和进位输出。

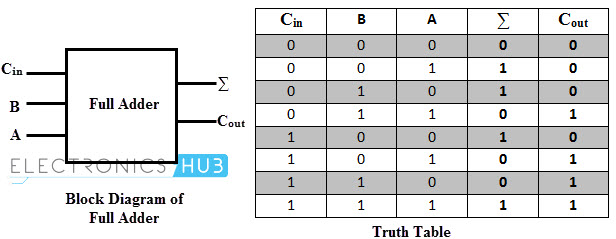

下图显示了一个完全加法器的框图,其中输入被标记为a、B和C在,而输出被标记为∑和C出.

说到真值表,下表显示了一个完全加法器的真值表。

| 输入 | 输出 | |||

| 一个 | B | C在 | 总和 | C出 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

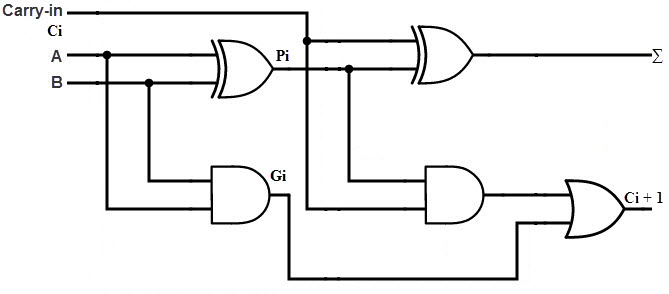

从上面的真值表中,我们可以得到Sum和进位输出的布尔表达式。利用这些表达式,我们可以构建全加法器的逻辑电路。但是,通过进一步简化方程,我们可以得出这样一个结论:使用两个半加法器和一个OR门,完全加法器可以很容易地实现。

下图展示了一个使用两个半加法器和一个OR门实现的全加法器电路。这里,A和B是主要的输入位C在进位输入是∑和C出分别是Sum和进位输出。

并行二进制蛇

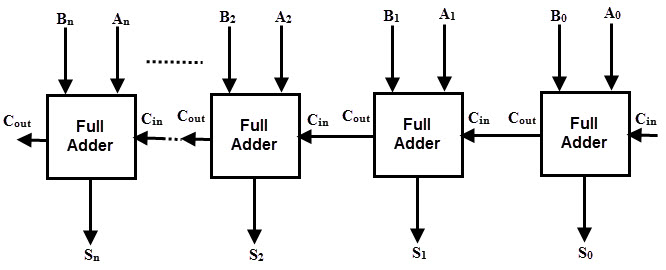

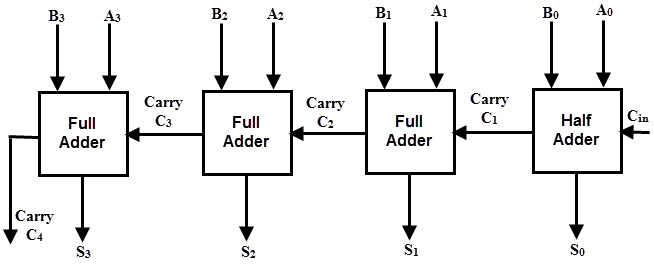

正如我们所讨论的,一个完整加法器执行两个一比特数和进位输入的相加。对于有一个以上位的二进制数的加法,需要一个以上的全加法器,而全加法器的数目取决于数字位。因此,并行加法器是多个完全加法器的组合,用于同时相加两个数字的所有位。

通过并联连接n个完全加法器,可以构造一个n位的并行加法器。从下图可以看出,在最小有效位置没有进位,因此我们可以使用半加法器或使全加法器在该位置的进位输入为零。

下图是一个并行4位二进制加法器,它有三个全加法器和一个半加法器。要相加的两个二进制数是“一个3.一个2一个1一个0”而且" B3.B2B1B0”,应用于全加法器的相应输入。这个并行加法器产生的结果是“C4年代3.年代2年代1年代0”,其中C4是最后的进位。

在4位加法器中,第一个块是半加法器,它有两个输入a0B0得到一个和S0和一个进位C1.第一个块也可以是一个完整的加法器,如果是这样,那么输入进位C0必须是0。

接下来的三个块应该是完全加法器,因为它们有三个输入(两个主要的二进制位和前一阶段的进位)。

因此,第二个块全加法器产生一个和S1a进位C2.接下来是另外两个完全加法器,因此最终的结果是C4年代3.年代2年代1年代0.

通常,全加法器设计在双列直插式封装集成电路中。74LS283是一种流行的4位全加法器集成电路。单元计算机的算术和逻辑单元(ALU)由这些并行加法器组成,用于执行二进制数的加法。

二进制减法电路

数字计算机执行的另一种基本算术运算是减法。减法是一种数学运算,从一个整数减去另一个整数以得到相等的数。要从其他数中扣除的数称为“被减数”,从被减数中减去的数称为“被减数”。

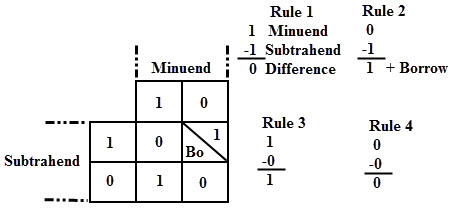

与二进制加法类似,二进制减法也是有四种可能的基本操作。它们是:

- 0 - 0 = 0

- 0 - 1 = 1

- 1 - 0 = 1

- 1 - 1 = 0

上图显示了二进制减法的四种可能的规则或基本操作。在所有操作中,减数位都从减数位扣除。

但在第二个规则中,减数位比减数位小,因此借1来执行减法。与加法器电路类似,基本减法电路也有两种类型:

- 半减法器

- 满减法器

半减法器

半减法器是一个多输出组合逻辑电路,它做两个1位二进制数字的减法。它有两个输入和两个输出。两个输入对应两个1位二进制数,两个输出对应差位和借位(与半加法器的和和进位相反)。

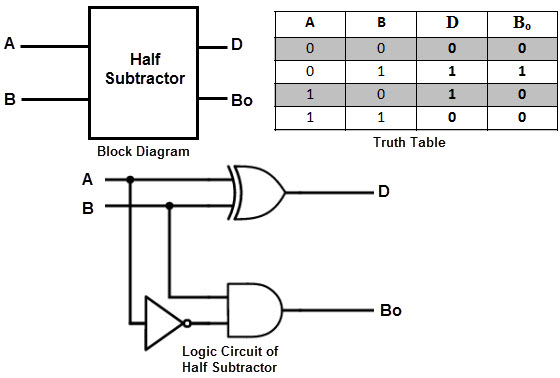

下图显示了半减法的框图。

图像

下表显示了半减法的真值表。

| 输入 | 输出 | ||

| 一个 | B | 区别 | 借 |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

根据上面的真值表,我们可以说,半减法的“差”输出类似于异或输出(这也与半加法的和输出相同)。因此,半减法也可以由具有一个反向输入和一个正常输入的与栅的出或栅来完成,这需要进行借置操作。

下图显示了半加法器的逻辑电路。

这种电路类似于半加法器,唯一的区别是被减数输入,即A在与门处被补以实现借位输出。

对于多位数的减法,两个数字之间的减法必须与前一个数字的减法的借位一起进行,因此减法器需要三个输入,这是用Half - subtractor无法实现的。因此,半减法的应用范围有限,严格地说,它在实践中不被使用。

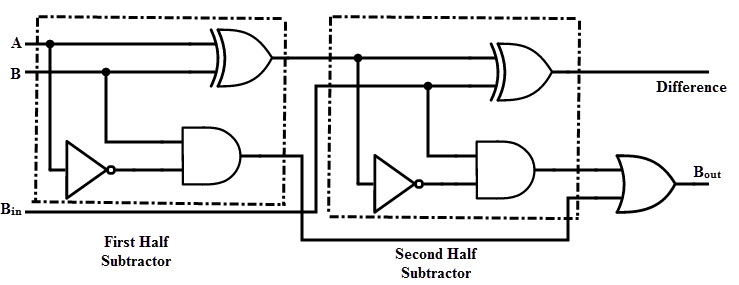

满减法器

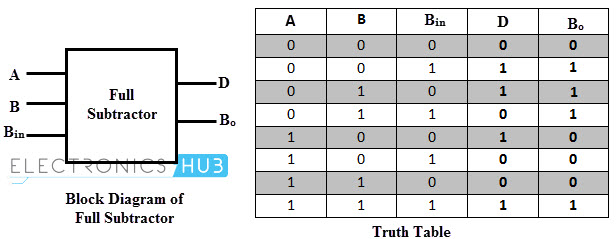

全减法是一种组合逻辑电路,它在两个1位二进制数之间进行减法,同时也考虑前一位的借位,即前一位的被减位是否借了1。

因此,一个完整的减法器有三个输入,其中两个输入对应被减法的两位(被减法的a和被减法的B),还有一个借位,通常表示为B在,对应于借操作。有两个输出,一个对应差值D输出,另一个对应借值B输出O.

下图显示了一个完整的减法器的框图。

下表显示了一个Full Subtractor的真值表。

| 输入 | 输出 | |||

| 一个 | B | B在 | D | B出 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

通过从上面的真值表推导出完整减法器的布尔表达式,我们得到的表达式告诉我们,一个完整的减法器可以用带OR门的一半减法器实现,如下图所示。

通过比较加、减电路和真值表,我们可以观察到,全减器的输出D与全加器的输出S完全相同。唯一的区别是输入变量A是对整个减法的补全。

因此,在将输入A加到门上产生最终借位输出Bo之前,只需对输入A进行互补,就可以将全加法器电路转换为全减法电路。

并行二进制减法器

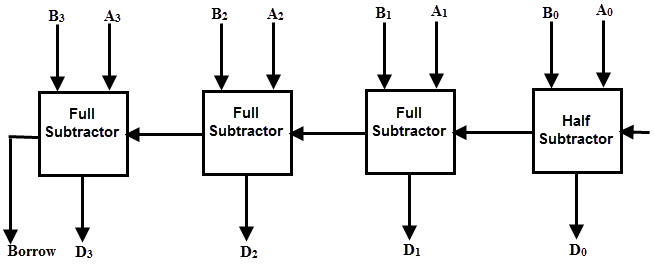

要对超过一位的二进制数进行减法运算,我们必须使用平行减法。这种并行减法器可以设计成多种方式,包括半全减法器组合、全全减法器、全全加法器和减法补输入等。

下图显示了一个4位并行二进制减法器,它由一个半减法器和三个全减法器连接而成。

在这个减法中,4位被减法“一个3.一个2一个1一个0”减去4位是减数吗" B3.B2B1B0”结果就是差值输出' D3.D2D1D0”.每个减法的借位输出作为借位输入连接到下一个减法。

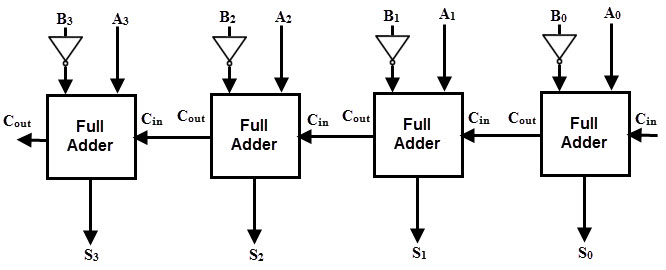

如图所示,使用4个全加法器设计4位并行减法器也是可能的。该电路考虑到被减数的加和被减数的补等于减法过程的原理,进行减法运算。

我们知道A减去B是用2的B的补数加上A得到的。2的B的补数是用1的补数加上最小有效位对得到的。

因此,在该电路中,通过逆变器(非门)得到B的补码1,并通过输入进位将1加到和上。

并行加/减

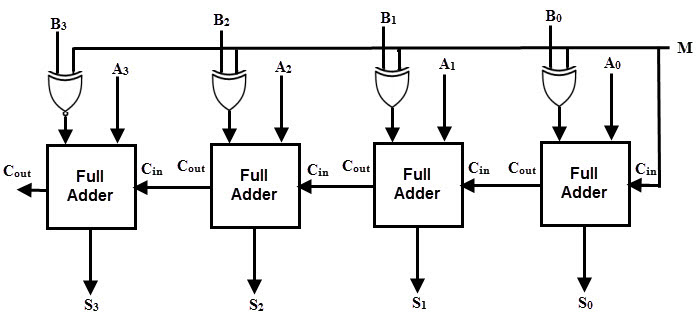

加法和减法的运算可以由一个普通的二进制加法器来完成。这种二进制电路可以通过在每个全加法器上加一个Ex-OR门来设计,如下图所示。下图显示了4位并行二进制加/减器,它有两个4位输入“一个3.一个2一个1一个0”而且" B3.B2B1B0”.

模式输入控制线M与全加法器的最低有效位进位输入相连接。这条控制线决定操作的类型,是加法还是减法。

当M= 1时,电路是减法器,当M=0时,电路是加法器。互接门由两个输入组成,其中一个与B相连,另一个与输入M相连。当M = 0时,B与0的互接产生B。然后,在进位输入为0的情况下,完全加法器将B与A相加,从而进行加法运算。

当M = 1时,0的B Ex-OR产生B补数,进位输入也为1。因此,补充的B输入被加到A中,1通过输入进位被加到A中,只有2的补操作。因此,执行减法操作。

结论

二进制加法器和减法器的一个完整的初学者教程。你们学习了不同的二进制加法器电路,如半加法器、全加法器、并行加法器,以及不同的二进制减法电路,如半减法器、全减法器、并行减法器,以及并行加/减组合电路。

16个反应

谢谢你!

伟大的. .很明确!谢谢(y)

谢谢,这真的很有用

非常感谢

这真的很有用,也很有意义,谢谢。

非常感谢

非常感谢

真的有用!用这个建立一个计算器在minecraft lol

我也是!

如果B >a和Cout在减法的情况下是“0”,S3S2S1S0是实际输出的2的补数。

在这种情况下,这个电路实际上不能描述所有情况下的减法,它仅限于A >b的减法

谢谢,非常感谢

非常感谢你。我在我的世界里找到了一个制作晶体管的方法,这个网站对我现在的计算器项目有很大的帮助。现在我只需要找出一种方法让它从十进制到二进制再转换回来。

感谢您提供的定义!非常满意!容易理解的

非常感谢

太好了,谢谢!

太好了!简洁明了,没有多余的废话(只是为了给人留下深刻印象)。

“Belal Igbal”的评论有一个有一个有效的观点。当(B > A)