本文介绍了数字秒表电路的原理,设计和操作。数字秒表可以是在几分钟,小时和秒内显示实际时间的电路,也可以是显示时钟脉冲数量的电路。在这里,我们设计了第二种类型,其中电路显示从0到59,代表60秒的间隔。换句话说,这里的电路仅在几秒钟内显示时间。这是一个由555个计时器组成的简单电路,用于产生时钟脉冲和两个计数器IC来进行计数操作。

数字秒表电路原理:

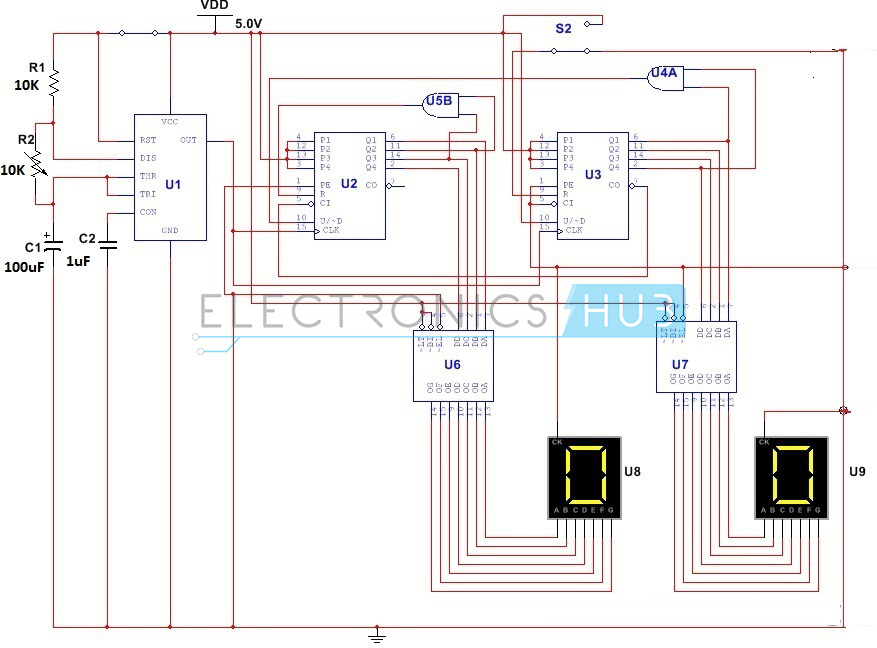

该电路基于基于同步级联的2阶段计数器操作的原理。这个想法是显示时钟脉冲的数量从0到59,代表60秒的间隔。这是通过使用以清晰模式连接的555个计时器IC来完成的,以产生每个间隔1秒间隔的时钟脉冲。虽然第一个计数器计数从0到9,但每次第一个计数器的计数值达到9时,第二个计数器开始其计数操作9.以级联格式连接的计数器IC,每个计数器输出都连接到BCD至7段解码器用于驱动7个段显示器。

数字秒表电路图:

数字秒表电路设计:

设计的第一部分涉及设计555计时器的敏感多启动器布置。在这里,所需的时间段为1秒。通过F = 1.44/(RA+RB)C给出的输出信号的频率,我们可以计算C的值,假设RA和RB的值约为10K。在这里,我们获得了100UF电解质电容器。

设计的第二部分涉及连接两个计数器IC - 4510以同步级联安排。这是通过将计数器的时钟引脚连接到555计时器的输出来实现的,从而产生了平行时钟输入信号。其中一个IC的进位销与另一个IC的销钉相连。

由于我们关注的是,一旦第一个计数器达到9的计数值,我们就开始使用第二个计数器,因此我们通过设计简单的组合逻辑电路来实现这一目标。从计数器真实表中召回,对于9的时钟脉冲计数,相应的二进制计数或计数器输出信号状态为1001。换句话说,计数为9,Q1和Q4处于高逻辑信号。在这里,我们使用的是AN和GATE IC 7408,其输入连接到第一个计数器的PINS Q1和Q4,并且输出连接到第二计数器的U/D引脚。

在这里,我们的要求是显示时钟脉冲直到计数为60。输入连接到第二个计数器的Q3和Q2。

第三部分涉及设计显示电路。这是通过将每个计数器的输出连接到BCD的输入到7个段解码器来完成的。每个解码器ICS 4511的输出连接到7个段显示。

数字秒表电路的工作:

一旦通常打开的开关更改为封闭位置,电路操作就会开始。计时器555以频繁的间隔产生高和低信号,导致振荡信号,其频率基于两个电阻和充电电容器的值。换句话说,计时器555 IC会产生所需时间段的时钟脉冲。该时钟信号被馈送到BCD计数器CD4510的两个阶段排列。IC CD4510由四个同步的D-触发器组成,它们连接在一起以实现计数操作。时钟脉冲由两个CD4510计数器的两个阶段同步级联排列计数。当IC U3接收到时钟脉冲时,它开始计数从0到9。一旦计数达到9,并且GATE IC U4A会产生高逻辑输出,该输出被馈送到IC U2的U/D引脚。IC U2开始计数操作。IC U2继续其计数操作,每次U3达到最终计数时,IC U3也是如此。但是,一旦IC U2计数达到6个计数,重置引脚就会由和门U5B设置为高级别。 The count is displayed on the 7 segment displays driven by the BCD to 7 segment decoders CD4511. The circuit thus displays the clock pulses from 0 to 60.

数字秒表应用程序:

- 该电路可以用作测验竞赛的指标。

数字秒表限制:

- 该电路没有显示实际时间,而是时钟脉冲的计数。

- 由于传播延迟,数字计数器的使用会导致整个操作的时间延迟。

- 这是一个理论电路,可能需要更改。

5个回应

我同意您的看法,非常感谢您分享了很棒的信息,您的人们很棒。

这个电路可以工作吗?

我连接了cirucuit,但即使给出了5 V,但也关闭了555个计时器。

嘿..您能够使它起作用吗?我的也只是显示零..倒计时:/

带有规范的组件列表。

只是为了你们的帮助!

组件列表如下:

U5B,U4A(IC 7408和GATE IC)

U1(IC 55计时器)

U2,U3(IC 4510)

U6,U7(IC 4511)

U8,U9(7段阴极)