介绍

相位锁定环或PLL是一个系统,该系统通常会参考通常来自晶体振荡器的输入信号。在本教程中,我们将看到如何在LPC2148中配置PLL并将其用作时钟生成器。

在讨论PLL之前,我们将在LPC2148和Crystal振荡器中看到时钟信号产生的一些基础。

LPC2148具有一个ON - 芯片振荡器,该振荡器与外部晶体振荡器在1 MHz至25 MHz范围内进行协调。如果fOSC是外部振荡器和CCLK输出的频率是处理器的时钟频率,然后是FOSC除非我们使用PLL,否则CCLK是相同的。

当我们使用PLL时,晶体振荡器的外时钟频率仅限于10 MHz至25 MHz的范围。该输入时钟频率乘以乘数和电流控制器振荡器(CCO)为10 MHz至60 MHz的范围。LPC214X MCUS系列中的最大工作频率限制为60 MHz。因此,PLL的最大输出为60 MHz。

LPC214X系列MCUS:PLL0和PLL1中有两个PLL模块。PLL0用于生成系统时钟,PLL1用于生成USB的时钟信号。PLL0和PLL1都接受10 MHz至24 MHz范围内的输入时钟信号,但PLL0的输出乘以10 MHz至60 MHz,而PLL1的输出对于USB时钟固定为48 MHz。

在本教程中,我们将仅关注PLL0,因为它是充当CPU时钟并继续使用的主时钟信号 - 芯片外围设备。如前所述,外部晶体的输入时钟频率在乘数和CCO的帮助下乘以乘以。乘数可以是1到32范围内的任何整数。实际上,由于CPU的上部频率限制为60 MHz,因此乘数值不能超过6。

当前的受控振荡器或CCO在156 MHz至320 MHz的频率范围内运行。为了将CCO保持在此范围内,使用PLL中的额外分离器。分隔线可以设置为除以1、2、4或8,以生成输出时钟频率。

在进一步配置PLL之前,我们将看到一些经常使用的符号,公式和标准值,如数据表中所述。

符号

| Fosc | 晶体振荡器的频率 |

| FCCO | 电流受控振荡器(CCO)的频率 |

| CCLK | CPU时钟频率(PLL输出频率) |

| m | PLL乘数值(在PLLCFG寄存器中使用MSEL位设置) |

| p | PLL分隔值(使用PLLCFG寄存器中的PSEL位设置) |

| PCLK | CCLK的外围钟 |

公式

CPU时钟的频率或PLL的输出为

cclk = m x fosc或cclk = fcco /(2 x p)

CCO的频率为

fcco = cclk x 2 x p或fcco = fosc x m x 2 x p p

标准值(使用PLL时)

- FOSC的范围为10 MHz至25 MHz

- CCLK的范围为10 MHz到F最大限度(LPC214X MCUS 60 MHz)

- FCCO的范围为156 MHz至320 MHz

设置PLL

笔记:为了使用PLL生成所需的时钟频率,我们需要操纵乘数和分隔线的值。这必须非常谨慎,因为PLL的输出充当了CPU的主时钟信号,并且还将给予其他ON -ON -ON - 在时钟信号下运行的芯片外围设备。

如果PLL错过 - 配置(意外或故意),则微控制器可能无法正常工作,并且用户负责。

来设置PLL,为避免意外错过 - PLL的配置,我们需要使用饲料序列。每当我们试图配置PLL时,都会初始化饲料序列。进料序列是解锁PLL配置的关键。

一个称为“ PLL0FEED”的特殊PLL相关寄存器用于设置饲料序列。为了设置馈电序列,必须分配两个固定值,即0xAA和0x55。

启动饲料顺序的代码是

PLL0FEED = 0xAA;

PLL0FEED = 0x55;

一旦我们成功初始化了进纸序列,就可以继续配置PLL。为此,我们需要了解我们将使用的其他PLL寄存器。

PLL控制寄存器(PLLCON):PLL控制寄存器或PLLCON寄存器包含用于“启用”和“连接” PLL的重点。PLLCON寄存器中的第一个位是PLL Enable(PLLE)位,第二位是PLL Connect(PLLC)位。

启用PLL意味着允许其锁定乘数和分隔线的值。连接PLL意味着允许CPU和其他 - 芯片外围设备将PLL的输出用作其时钟信号。

该寄存器的语法是PLLXCON,其中“ X”是PLL模块,即PLL0的PLL0CON和PLL1的PLL1CON。

笔记:将在文章的其余部分中遵循类似的命名法,其中任何相关寄存器中的“ X”用于指示PLL块,即PLL0的“ X” = 0,而PLL1的“ X” = 1。

PLL配置寄存器(PLLXCFG):PLL配置寄存器用于存储PLL的乘数和分隔值。只有在给出正确的饲料序列时,PLLCFG寄存器中的值才能实现。

PLLCFG寄存器中的前五位(称为MSEL)用于存储乘数(M)的值。接下来的两个位称为PSEL,用于存储分隔符(P)值。

PLL状态登记册(PLLXSTAT):PLL状态寄存器是一个读取 - 仅提供使用其他PLL寄存器设置的PLL参数的寄存器。如果给出有关MSEL(乘数),PSEL(Divider),PLLE(PLL启用),PLLC(PLL Connect)和PLOCK的详细信息。

我们必须关注的主要位置在PLLSTAT寄存器中是11Th位,即plock。PLOCK位指示PLL的锁状态。仅当PLL锁定到所需的频率时,Plock位才变为“ 1”。

必须遵循以下设置顺序,以便为所需频率配置PLL。

- 设置PLL

- 锁定PLL的饲料顺序

- 等待PLL锁定到所需的频率

- 连接PLL

- 将PLL设置为系统时钟的馈送顺序

我们以前已经看到了如何应用饲料序列。现在,我们将进一步移动,看看如何配置PLL。

确定PLL设置的过程

我们需要为PLL0执行以下步骤。

- 选择所需的系统频率(CCLK)。系统时钟可能基于处理器吞吐量,uart波特率,等等。

- 选择晶体振荡器(FOSC)的输入频率。系统时钟(CCLK)必须是振荡器频率(FOSC)的倍数。

- 计算乘数(M)的值并配置MSEL位。从上面提到的公式中,M = CCLK / FOSC(M的范围为1至32)。从这个“ M”值中,我们需要将MSEL位在PLL0CFG寄存器中写入“ M-1”。

- 计算分隔线(P)的值并配置PSEL位。选择分隔器以使CCO(FCCO)的频率处于极限(156 MHz至320 MHz)。“ P”的值可以为1、2、4或8。

让我们假设CPU频率为最大可能值,即60 MHz。我们将在此频率上计算P和M的值。

首先,我们将根据不同的“ P”值看到PSEL的可能值。

| p | PSEL中的二进制值(PLL0CFG中的位5和6) |

| 1 | 00 |

| 2 | 01 |

| 4 | 10 |

| 8 | 11 |

由于CCLK = 60 MHz,因此我们可以按以下方式计算P的值。计算p的方程式由

P = FCCO /(2 x CCLK)

我们知道,FCCO的范围为156 MHz至320 MHz。

替换FCCO = 156 MHz,我们得到P = 156 MHz /(2 x 60 MHz)= 1.3。

替换FCCO = 320 MHz,我们得到P = 320 MHz /(2 x 60 MHz)= 2.67。

由于“ P”的值必须是整数,因此1.3和2.6之间的整数为“ 2”。

当我们获得“ P”为“ 2”的值时,PSEL位中的值应为“ 01”。

现在,我们将计算“ M”的值。根据上述公式,我们可以使用以下公式计算“ M”的值。

M = CCLK / FOSC

下表表示可能的晶体振荡器值列表以及“ M”,“ MSEL”,“ P”,“ PSEL”的值以及PLL0CFG寄存器中的值。

| Fosc | m | MSEL(M -1)中的价值 | p | psel中的价值 | PLL0CFG中的价值 |

| 5 MHz | 12 | 11 = 0xB | 2 | 01 | 0x2b |

| 10 MHz | 6 | 5 = 0x5 | 2 | 01 | 0x25 |

| 12 MHz | 5 | 4 = 0x4 | 2 | 01 | 0x24 |

| 15 MHz | 4 | 3 = 0x3 | 2 | 01 | 0x23 |

| 20 MHz | 3 | 2 = 0x2 | 2 | 01 | 0x22 |

外围钟(PCLK)

来自PLL的时钟信号作为其时钟传递给CPU。PLL信号还必须在其他芯片外围设备上提供。默认情况下,外围时钟(PCLK)以CCLK的四分之一速度运行。可以使用称为“ VPBDIV”的特殊寄存器(按KEIL编译器)配置CPU时钟和外围时钟之间的关系。

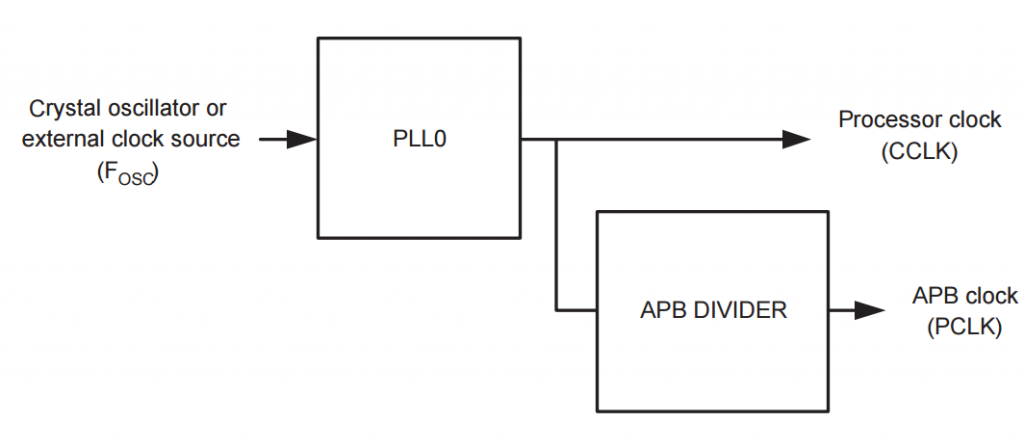

下图显示了PLL,CCLK和PCLK的框图。

VPBDIV寄存器中的值确定PCLK值。下表显示了VPBDIV和相应的PCLK值的可能值。

| VPBDIV = 0x00 | PCLK是CCLK的1/4 |

| VPBDIV = 0x01 | PCLK等于CCLK |

| VPBDIV = 0x02 | PCLK是CCLK的½ |

| VPBDIV = 0x03 | 预订的。没有效果。 |

我们已经看到了所有寄存器,设置和必要的计算,以配置PLL0。有关此的更多信息,我们可以查看MCUS的LPC214X系列的数据表和用户手册。

现在,我们将看到一个用于配置PLL0的示例程序,以便CPU时钟(CCLK)和外围时钟(PCLK)必须在60 MHz下运行,外部晶体振荡器在12 MHz下运行。

笔记:12 MHz是许多微控制器开发板中晶体振荡器的最常见值。如果您使用的开发具有不同的晶体振荡器(出于某种奇怪的原因),那么我们需要考虑“ M”和“ P”的值。

#Define Plock 0x00000400

int main(void)

{

/* pple = 1且pplc = 0,因此将启用PLL0但未连接。*/

PLL0CON = 0x01;

/* PLL0CFG按照上述表设置。*/

PLL0CFG = 0x24;

/ *将PLL0锁定到所需频率的进料序列 */

PLL0FEED = 0xAA;

PLL0FEED = 0x55;

/*通过阅读锁定位检查PLL0是否已锁定到所需频率

在PPL0STAT寄存器中 */

while(!(pll0stat&plock));

/ *现在启用(再次)并连接PLL0 */

PLL0CON = 0x03;

/ *用于将PLL0连接为系统时钟的供稿序列 */

PLL0FEED = 0xAA;

PLL0FEED = 0x55;

/*现在系统时钟正在运行 @ 60 MHz!下一步是将外围时钟设置为与系统时钟相同的频率 */

VPBDIV = 0x01;

而(1);

}

3个回应

非常精确的解释!非常感谢

非常感谢您的出色解释

这正是我正在寻找的…………..非常深刻的解释,这使整个话题太容易理解了…………..谢谢你如此多